## AMERICAN DATA DIVISION AIRPAX ELECTRONICS, INC.

MATRIX

HUNTSVILLE, ALABAMA

401 WYNN DRIVE, N.W. P. O. BOX 5228 HUNTSVILLE, ALABAMA 35805 PHONE (205) 837-5180

### INSTRUCTION MANUAL

SERIES 900/900E

#### VIDEO/AUDIO SIGNAL ROUTING SWITCHER

-0-

Stock W/O Authorization #2735

Cy <u>25</u> of 25

## AMERICAN DATA DIVISION

401 WYNN DRIVE • P. O. BOX 5228 • HUNTSVILLE, ALABAMA 35805 USA • TELEPHONE 205 837-5180 • TWX 810 726-2125

#### TABLE OF CONTENTS

#### SECTION 1 - INTRODUCTION

|       | Description                                                                                                                     | 1                          |

|-------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| SECTI | ION 2 – INSTALLATION                                                                                                            |                            |

|       | General<br>Inspection<br>Unpacking, Damage and Shipping<br>Power Requirements<br>Installation                                   | 2<br>2<br>3<br>3           |

| SECT  | ION 3 - SPECIFICATIONS                                                                                                          |                            |

|       | Electrical<br>Video<br>Audio<br>Environmental<br>900E Specifications                                                            | 5<br>5<br>7<br>7<br>8      |

| SECTI | ION 4 - REFERENCE DATA                                                                                                          |                            |

|       | Video Levels<br>DB Voltage Ratio as Related to IEEE Units<br>and Percentage                                                     | 9                          |

|       | Propagation Delay Through Coaxial Cable<br>Data Sheets                                                                          | 10<br>13-25                |

| SECT  | ION 5 - CIRCUIT DESCRIPTIONS                                                                                                    |                            |

|       | l x 10 Audio/Video Crosspoint Card<br>Audio/Video Output Amplifier<br>Matrix Control Logic<br>Control Interface<br>Power Supply | 26<br>27<br>28<br>30<br>31 |

Page

Page

#### SECTION 6 - MAINTENANCE

| General Data | 32 |

|--------------|----|

| Test Data    | 35 |

#### SECTION 7 - COMPONENT LAYOUTS, PARTS LISTS AND WIRING LISTS

| List of Component Layouts | 39    |

|---------------------------|-------|

| List of Wiring Lists      | 39    |

| List of Parts Lists       | 39    |

| Wiring Lists              | 40-46 |

| Parts Lists               | 47-51 |

Series 900/900E Basic Document: 4/75 Last Printing: 6/76

#### SECTION 1 - INTRODUCTION

#### Description

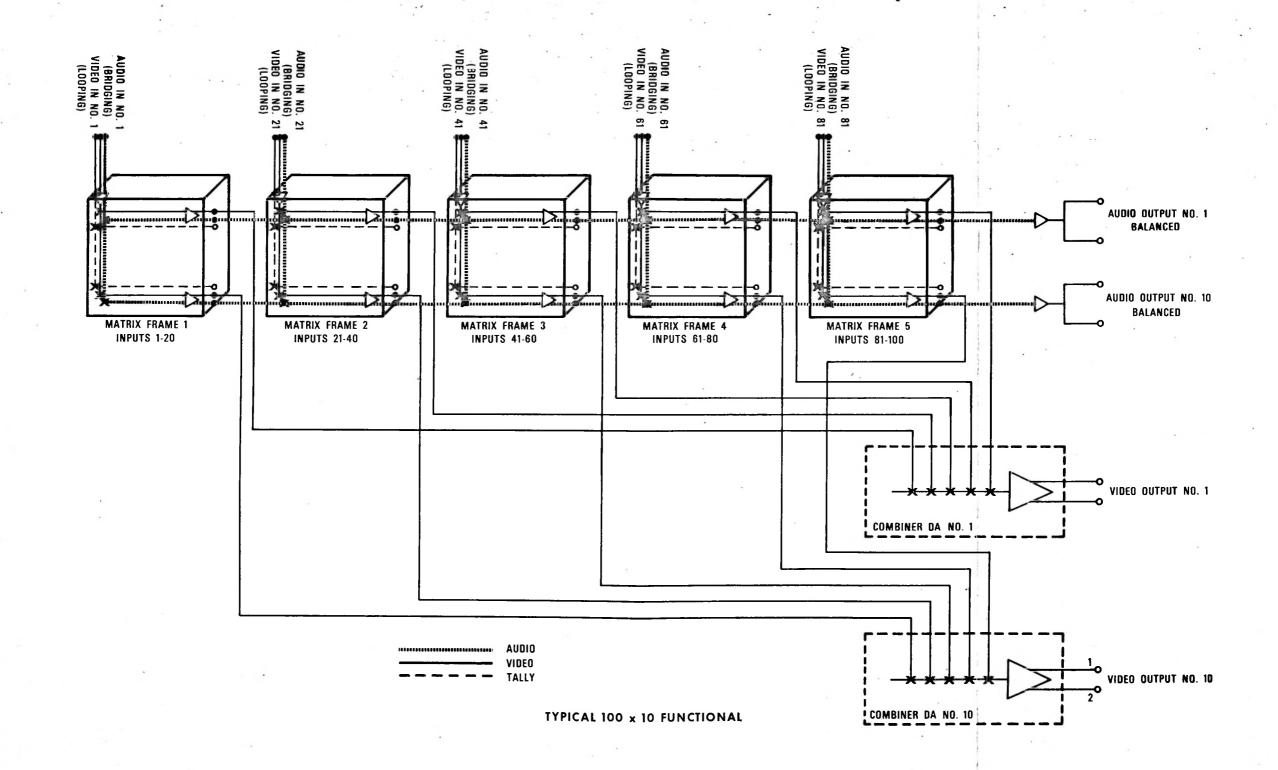

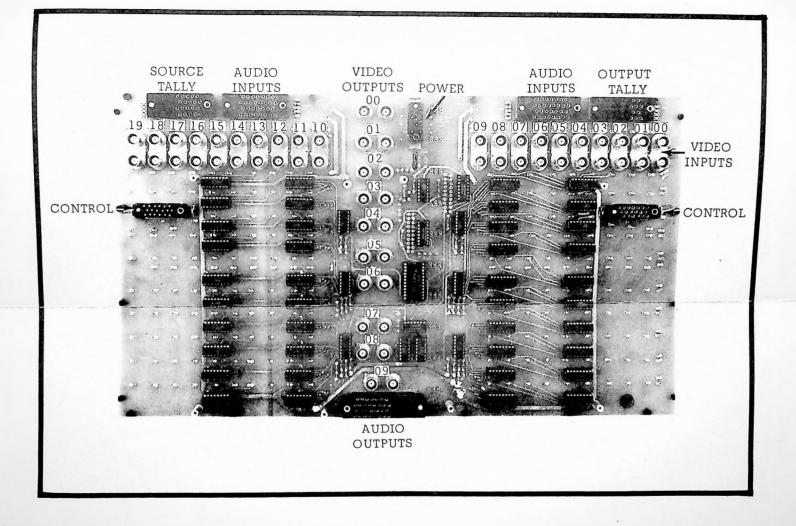

The series 900/900E matrix frame is a video-audio-tally routing switcher with up to twenty inputs and up to ten outputs per frame assembly. Frame assemblies are combined horizontally by means of combiner amplifiers to create routing systems larger than  $20 \times 10$ . High input impedance and a low reflection factor allow more than one box to be looped through vertically to form  $20 \times 20$ 's,  $20 \times 30$ 's, etc. Up to ten frames can be tied together vertically to provide a  $1 \times 100$  configuration. A typical  $100 \times 10$  configuration is shown in the block diagram, "Typical  $100 \times 10$  Functional".

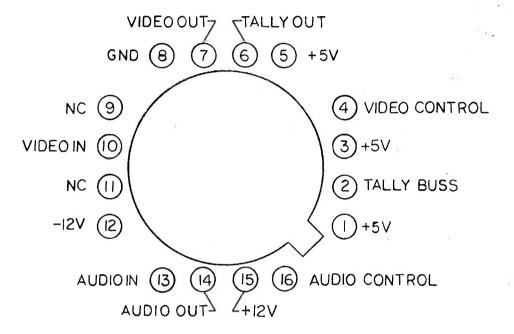

Video input and output connections are made through BNC connectors located on the back plane of the routing switcher. Audio input and output connections are made through AMP multipin connectors with press lock retaining mechanisms. Control inputs, tally outputs and power inputs are also made through AMP connectors on the back plane with press lock retaining mechanisms.

The fundamental 20 x 10 series 900/900E matrix is controllable by one 16-bit BCD word, <u>or</u> by individual bus 8-bit BCD words, <u>or</u> by 20 discrete control lines for each output bus. ADC offers a number of control methods for the matrix or a number of matrices. Details on controls are normally contained in the systems manual and in the individual control instruction manual.

For matrix arrangements of 20 x 20 and smaller, ADC normally supplies a standard ADC Model 501 power supply. For larger matrix arrangements, purchased Lambda, Hewlett-Packard, or equivalent supplies are provided. In the case of purchased supplies, the manufacturer's standard manual will be supplied.

The basic series 900/900E matrix frame is 10.5 inches high and mounts in a standard 19 inch relay rack. Each matrix frame contains up to twenty 1 x 10 audio/video crosspoint cards and up to ten audio/video output amplifiers. These cards can be easily removed for maintenance or replacement and can generally be moved to other locations in the matrix with very little effect on system performance.

#### SECTION 2 - INSTALLATION

#### <u>General</u>

The series 900/900E audio/video routing switcher is carefully inspected, tested and calibrated before shipment to insure years of stable, trouble-free service. Each frame requires 10.5 inches of vertical space in a standard 19 inch relay rack. No special cooling requirements are necessary since it was designed to operate in a temperature range from  $0^{\circ}$  to  $50^{\circ}$  C. However, care should be taken to prevent an excessive ambient heat rise in closed, unventilated equipment racks. This is especially true if this equipment is installed in the same rack with vacuum tube equipment.

#### **Inspection**

Immediately upon receipt, inspect the packing boxes or crates for external signs of abusive handling. If such a condition is noted, notify the carrier immediately. If no external damage is visible, remove the packing material from around the matrix frame(s), control panel(s) and power supplies. Inspect to see that all PC boards are installed properly in their respective connectors and are securely fastened. Make a check of all equipment for any visible damage which may have occurred during transit.

#### Unpacking, Damage and Shipping

While unpacking and checking the various modules against the packing list, you may find it to your advantage to mount them in the equipment rack as you progress. The cable layout supplied must be utilized so that cable lengths will be long enough.

#### CAUTION

#### Do not interchange or substitute coax cables as marked. System timing will be affected.

Any variation from the specified inventory should be reported to ADC immediately. Write to: American Data Corporation, 401 Wynn Drive NE, P. O. Box 5228, Huntsville, Alabama 35805. If shipment damage is incurred, obtain a report from your express agent or trucker and mail it to the address indicated earlier. Do not return damaged parted until instructed to do so by ADC.

If electronic units must be returned for service, tag them with your name, complete address, and exact description of difficulties encountered. Use original shipping cartons, if possible. If they are not available, wrap the unit in heavy paper before placing it in a carton which should be large enough to permit the use of at least three inches of shredded paper or excelsion between all sides of the unit and the carton. Mark the carton <u>FRAGILE</u> and clearly address it as shown earlier. Include your own name and address on the carton and ship by prepaid express. The unit will be returned express collect. Bear in mind that the carrier will disclaim responsibility for damage if, in his opinion, it was caused by improper packing.

#### Power Requirements

AC voltage - 105 to 125 volts ac, 60 Hz or 200 to 240 volts ac, 50 Hz (on special order). The equipment is normally wired for ac supply voltages of 105 to 125 volts (117 volts ac nominal), 50 to 60 Hz, unless otherwise specified. Current limiting is used on all the dc outputs providing brief short-circuit protection. Primary ac is fused against excessive current drains.

A three wire ac plug is provided for protection against accidental power shorts to chassis. In no case should the three wire plug be removed or tampered with.

#### Installation

The series 900/900E Routing Switchers are available in many configurations, making it impossible to include all installation directions in the instruction manual. A system connection diagram will be supplied for systems having more than one matrix frame. Care must be exercised in following instructions for system connections since system timing can be dramatically affected by intermixing video cables. Standard "good commerical practices" should be used in cabling, service loops, cable supports, etc. Should any difficulty be encountered with the installation or during initial system tests, please contact ADC immediately.

After you have completed visual inspection and installation of the equipment, ADC suggests that you apply a 1 volt p-p signal to all video inputs and an 8 dBm audio signal to all audio inputs, then switch each input (audio and video) to each output. This will functionally test all the control logic, each crosspoint (audio and video) and all output amplifiers. <u>Do not attempt to adjust GAIN</u>, <u>PHASE or RESPONSE controls at this time</u>. In the event that a discrepancy is noted, make a note of it and follow the maintenance procedure given in Section 6 of this instruction manual.

#### SECTION 3 - SPECIFICATIONS

Electrical

Power - ac

Power - dc

105 - 125 volts ac, 50 - 60 Hz or 200 - 240 volts ac, 45 - 55 Hz (on order)

+12 volts dc battery (optional) to keep the crosspoints latched in the event of power failure.

#### Video

Input

| Signal level | l volt p-p video            |

|--------------|-----------------------------|

| Impedance    | 50 K ohm - bridging         |

| Return loss  | Greater than 45 dB to 5 MHz |

Number of inputs Up to 20 per bus (basic frame) audio/video

#### Output

Level

Impedance

Number of outputs per bus

Isolation between outputs

Level difference

DC on output

Frequency response

l volt p-p

75 ohms

Two

Greater than 36 dB to 4.2 MHz

Less than 1%

Less than 0.05 volts

$\pm 0.1 \text{ dB to 5 MHz}$  $\pm 0.5 \text{ dB to 8 MHz}$ Less than -1.0 dB at 10 MHz

Hum (peak to peak)

Greater than 60 dB below output

Bounce (10% - 90% APL)

Gain

Linear chroma distortion (MOD 20T pulse, 1/2 line pulse)

Line tilt

Field tilt

Differential gain (10% - 90% APL)

Differential phase (10% - 90% APL)

Maximum axis shift

Amplitude stability

Less than 0.1 volt

Nominal - unity, adjustable +3 dB

$\pm 0.1$  dB relative chroma level  $\pm 10$  ns relative chroma time

Less than 0.5%

Less than 1.0%

Less than 0.5%

Less than 0.5°

Less than 0.1 volt

Less than 0.1 sec

Less than 0.1% for <u>+</u>10% line voltage change Less than 0.25% for 24 hours

Greater than 60 dB at 3.58 MHz

Greater than 56 dB at 4,43 MHz

+1.0<sup>0</sup> (3.58 MHz or 4.43 MHz)

Switching time

Crosstalk

Path length accuracy (all inputs to any output)

#### Audio

Input

Signal level-10 to +18 dBm, +8 dBm nominalImpedance600 ohms balanced or high<br/>impedance bridging

Number of inputs

Up to 20 per bus

· · · · · ·

Output

Signal level

Number of outputs

Impedance

Frequency response (reference 1 kHz)

Harmonic distortion (+18 dBm output)

Signal-to-noise ratio (20 Hz to 20 kHz)

Gain

Switching time

Crosstalk (20 Hz to 20 kHz)

Common mode rejection

Maximum common mode voltage

Environmental

Operating temperature range

Storage temperature range

Control

Control voltage (ON)

Control voltage (OFF)

+8 dBm nominal, +18 dBm maximum

One

600 ohms balanced

+0.5 dB, 20 Hz to 20 kHz

Less than 0.5% from 20 Hz to 20 kHz

Greater than 75 dB below +18 dBm output

20 dB nominal

Less than 0.1 sec

Greater than 70 dB below +18 dBm

Greater than 60 dB at 60 Hz

24 volts p-p

$0^{\circ}$  to +60° C

$-20^{\circ}$  to  $+70^{\circ}$  C

Momentary single pole closure to matrix ground (2.5 mA)

+5 volts dc

7

#### 900E Specifications

The series 900E is configured identically to the professional series. System specifications are reduced on the following parameters to:

| Crosstalk (3.58 or 4.43 MHz)           | Greater than 50 dB       |

|----------------------------------------|--------------------------|

| Differential phase<br>(10% to 90% APL) | Less than 1 <sup>0</sup> |

| Differential gain<br>(10% to 90% APL)  | Less than 1%             |

Path length accuracy

Signal-to-noise ratio

Audio frequency response

Audio distortion

Audio signal-to-noise ratio

Within <u>+</u>20

Greater than -52 dB

<u>+1</u> dB (20 Hz to 20 kHz)

Less than 1% (20 Hz to 20 kHz)

Greater than -65 dB below +18 dBm

Audio crosstalk

Greater than -60 dB below +18 dBm

#### SECTION 4 - REFERENCE DATA

#### VIDEO LEVELS

|                       |      |            | <br>       |       |

|-----------------------|------|------------|------------|-------|

| Composite Video Level | 140  | IEEE Units | <br>1.0    | Vp-p  |

| Picture Signal        | 90   | IEEE Units | <br>0.642  | Vp-p  |

|                       | 92.5 | IEEE Units | <br>0.66   | Vp-p  |

| Set Up                | 10   | IEEE Units | <br>0.0714 | V р-р |

|                       | 7.5  | IEEE Units | <br>0.0535 | V р-р |

| Synchronizing Pulses  | 40   | IEEE Units | <br>0.285  | Vp-p  |

#### DB VOLTAGE RATIO AS RELATED TO IEEE UNITS AND PERCENTAGE

| IEEE Units Down | dB   | % Dor | wn From | dB   |

|-----------------|------|-------|---------|------|

| From 140 Units  | Down | 100 U | Inits   | Down |

|                 |      |       |         |      |

| 2               | 0.1  | 1%    |         | 0.08 |

| 5               | 0.3  | 2%    |         | 0.17 |

| 10              | 0.7  | 3%    |         | 0.25 |

| 15              | 1.0  | 4%    |         | 0.34 |

| 20              | 1.4  | 5%    |         | 0.42 |

| 30              | 2.1  | 10%   |         | 0.90 |

| 40              | 2.9  | 15%   |         | 1.4  |

| 50              | 3.8  | 20%   |         | 1.93 |

| 60              | 4.8  | 25%   |         | 2.5  |

| 70              | 6.0  | 30%   |         | 3.04 |

| 80              | 7.4  | 40%   |         | 4.40 |

| 90              | 8.9  | 50%   |         | 6.02 |

| 100             | 10.9 | 60%   |         | 8.0  |

| 110             | 13.4 | 70%   |         | 10.4 |

| 120             | 16.9 | 80%   |         | 14.0 |

| 130             | 22.9 | 90%   |         | 20.0 |

#### PROPAGATION DELAY THROUGH COAXIAL CABLE

Velocity of Propagation (VP) in solid polyethylene dielectric coaxial cable is 66% of velocity in free space. This is equal to 7.874 inches per nanosecond, 20.000 cm per nanosecond. Practical figures are:

> 8" (20 cm) coaxial cable = 1 nanosecond 6" (15.4 cm) coaxial cable =  $1^{\circ}$  at 3.58 MHz T at 3.58 MHz = 279 nanoseconds T per degree at 3.58 MHz = 0.77 nanosecond

| 1  | nsec | = | 1,28 <sup>0</sup>  | = | 7.9"  | (20 cm) |

|----|------|---|--------------------|---|-------|---------|

| 2  | nsec | = | 2,56 <sup>0</sup>  | = | 15.7" | (40 cm) |

| 3  | nsec | = | 3.84 <sup>0</sup>  | = | 23.6" | (60 cm) |

| 4  | nsec | = | 5.12 <sup>0</sup>  | = | 31.5" | (80 cm) |

| 5  | nsec | = | 6,40 <sup>0</sup>  | = | 39.4" | (lm)    |

| 6  | nsec | = | 7,68 <sup>0</sup>  | = | 47.2" | (1.2 m) |

| 7  | nsec | = | 8,96 <sup>0</sup>  | = | 55.1" | (1.4 m) |

| 8  | nsec | = | 10.24 <sup>0</sup> | = | 63.0" | (1,6 m) |

| 9  | nsec | = | 11.52 <sup>0</sup> | = | 70.9" | (1.8 m) |

| 10 | nsec | = | 12.80 <sup>0</sup> | = | 78.7" | (2.0 m) |

|    |      |   |                    |   |       |         |

| =   | 6,1"       | ( 15.4 cm)                                                                                                                 |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------|

| =   | 30.3"      | ( 77.0 cm)                                                                                                                 |

| =   |            | (1 m 54.0 cm)                                                                                                              |

| =   | 7' 6,9"    | (2 m 31.0 cm)                                                                                                              |

| =   | 10' 1.3"   | (3 m 8.0 cm)                                                                                                               |

| =   | 12' 7.6"   | (3 m 85.0 cm)                                                                                                              |

| =   | 15' 1.9"   | (4 m 62.0 cm)                                                                                                              |

| =   | 30' 3.8"   | (9 m 24.0 cm)                                                                                                              |

| =   | 45' 5,7"   | (13 m 86.0 cm)                                                                                                             |

| =   | 90'11.3"   | (27 m 72.0 cm)                                                                                                             |

| = . | 136' 5,0"  | (41 m 58.0 cm)                                                                                                             |

| =   | 181' 10,7" | (55 m 44.0 cm)                                                                                                             |

|     |            | = 30.3" $= 60.6"$ $= 7' 6.9"$ $= 10' 1.3"$ $= 12' 7.6"$ $= 15' 1.9"$ $= 30' 3.8"$ $= 45' 5.7"$ $= 90' 11.3"$ $= 136' 5.0"$ |

A D C CROSSPOINT TYPE I

Fig. 4-1 HYBRID CROSSPOINT

A D C CROSSPOINT

Fig. 4-2 MONOLITHIC CROSSPOINT

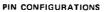

#### QUADRUPLE 2-INPUT POSITIVE **S5400** NAND GATE N7400

\$5400-A,F,W . N7400-A,F DIGITAL 54/74 TTL SERIES

PIN CONFIGURATIONS

#### **RECOMMENDED OPERATING CONDITIONS**

|                                                                   |                                  | MIN | NOM      | мах         | UNIT   |

|-------------------------------------------------------------------|----------------------------------|-----|----------|-------------|--------|

| Supply Voltage V <sub>CC</sub> : S5400 Circuits<br>N7400 Circuits |                                  | 45  | 5        | 5 5<br>5.25 | v      |

| Normalized Fan-Out from each Output, N                            |                                  |     | -        | 10          |        |

| Operating Free-Air Temperature Range, T <sub>A</sub> :            | S5400 Circuits<br>N7400 Circuits | -55 | 25<br>25 | 125<br>70   | c<br>c |

|                                                                   |                                  |     |          | 1           | 3      |

ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

| PARAMETER           |                                                                                                        | TEST CONDITIONS                                    |                                                  | •              | MIN          | TYP" | MAX        | UNIT     |  |

|---------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------|----------------|--------------|------|------------|----------|--|

| V <sub>in(1)</sub>  | Logical 1 input voltage<br>required at both input<br>terminals to ensure<br>logical 0 level at output  | V <sub>CC</sub> = MIN                              |                                                  |                | . 2          |      |            | . v      |  |

| V <sub>in(0)</sub>  | Logical 0 input voltage<br>requited at either input<br>terminal to ensure<br>logical 1 level at output |                                                    |                                                  |                |              |      | 0.8        | v        |  |

| V <sub>out(1)</sub> | Logical 1 output voltage                                                                               | $V_{CC} = MIN,$<br>$I_{load} = -400\mu A$          | V <sub>in</sub> = 0.8V,                          |                | 2.4          | 3.3  |            | v        |  |

| V <sub>out(0)</sub> | Logical 0 output voltage                                                                               | V <sub>CC</sub> = MIN,<br>I <sub>sink</sub> = 16mA | V <sub>in</sub> ≈ 2V,                            |                |              | 0.22 | 04         | v        |  |

| tin(0)              | Logical O level input<br>current (each input)                                                          | VCC MAX.                                           | V <sub>in</sub>                                  |                |              |      | -1.6       | mA       |  |

| lin(1)              | Logical 1 level input<br>current (each input)                                                          | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX,   | V <sub>tn</sub> ≓ 2.4V<br>V <sub>tn</sub> ≈ 5.5V |                |              |      | 40<br>I    | µA<br>mA |  |

| 'os                 | Short circuit output<br>current <sup>†</sup>                                                           | VCC = MAX                                          |                                                  | S5400<br>N7400 | - 20<br>- 13 |      | -55<br>-55 | mΑ       |  |

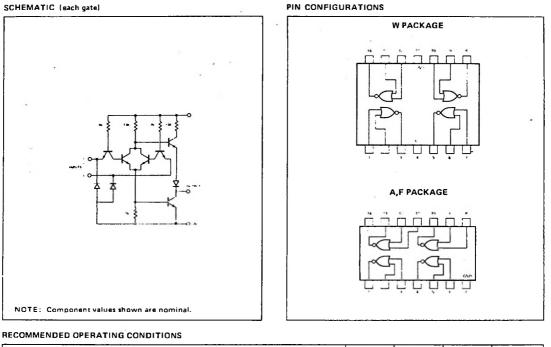

## QUADRUPLE 2-INPUT POSITIVE NOR GATE | S5402

#### S5402-A,F,W . N7402-A,F

N7402

#### DIGITAL 54/74 TTL SERIES

|                                                 |                | MIN  | NOM | MAX  | UNIT |

|-------------------------------------------------|----------------|------|-----|------|------|

| Supply Voltage V <sub>CC</sub> : S5402 Circuits |                | 4.5  | 5   | 5.5  | v    |

| N7402 Circuits                                  |                | 4.75 | 5   | 5.25 | v    |

| Normalized Fan-Out from each Output, N          |                |      |     | 10   |      |

| Operating Free-Air Temperature Range, TA:       | S5402 Circuits | -55  | 25  | 125  | °c   |

|                                                 | N7402 Circuits | 0    | 25  | 70   | °C   |

|                                                 |                |      |     |      |      |

ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

|                     | PARAMETER                                                                                              | TEST                                                 | CONDITIONS                                       |              | MIN        | TYP  | мах             | UNIT     |

|---------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------|--------------|------------|------|-----------------|----------|

| Vin(1)              | Logical 1 input voltage<br>required at either input<br>terminal to ensure<br>logical 0 level at output | V <sub>CC</sub> = MIN                                |                                                  |              | 2          |      |                 | v        |

| V <sub>in</sub> (0) | Logical 0 input voltage<br>required at both input<br>terminals to ensure<br>logical 1 level at output  | V <sub>CC</sub> = MIN                                |                                                  |              |            |      | 0.8             | v        |

| V <sub>out(1)</sub> | Logical 1 output voltage                                                                               | V <sub>CC</sub> = MIN,<br><sup>1</sup> load = -400µA | V <sub>10</sub> = 0.8V                           |              | 2.4        | 3.3  |                 | v        |

| Vout(0)             | Logical O output voltage                                                                               | V <sub>CC</sub> = MIN,<br>  I <sub>sink</sub> = 16mA | V <sub>in</sub> ≈ 2V,                            |              |            | 0.22 | 0.4             | v        |

| lin(0)              | Logical O level input<br>current (each input)                                                          | V <sub>CC</sub> = MAX,                               | V <sub>in</sub> = 0,4V                           |              |            |      | -1.6            | mA       |

| lin(1)              | Logical 1 level input<br>current (each input)                                                          | V <sub>CC</sub> = MAX.<br>V <sub>CC</sub> = MAX,     | V <sub>in</sub> ≖ 2.4V<br>V <sub>in</sub> = 5.5V |              |            |      | <b>4</b> 0<br>1 | μA<br>mA |

| IOS                 | Short circuit output<br>Current†                                                                       | V <sub>CC</sub> - MAX                                | -                                                | 5402<br>7402 | -20<br>-18 |      | -55<br>-55      | mA       |

|                                                          | MIN  | NOM | MAX  | UNIT |

|----------------------------------------------------------|------|-----|------|------|

| Supply Voltage V <sub>CC</sub> : S5404 Circuits          | 4.5  | 5   | 5.5  | v    |

| N7404 Circuits                                           | 4.75 | 5   | 5.25 | v    |

| Normalized Fan-Out from Output, N                        |      |     | 10   |      |

| Operating Free-Air Temporature Range, TA: S5404 Circuits | -55  | 25  | 125  | .C   |

| N7404 Circuits                                           | 0    | 25  | 70   | °C   |

ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

|                        | PARAMETER                                                                                           | TEST                                                          | CONDITIONS                                       |                 | MIN        | TYP'' | MAX        | UNIT     |

|------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------|-----------------|------------|-------|------------|----------|

| <br>V <sub>in(1)</sub> | Logical 1 input voltage<br>required at input<br>terminal to ensure logi-<br>cal 0 level at output   | V <sub>CC</sub> <sup>z</sup> MIN                              |                                                  |                 | 2          |       |            | v        |

| V <sub>in(0)</sub>     | Logical O input voltage<br>required at any input<br>terminal to ensure<br>logical 1 level at output | VCC * MIN                                                     |                                                  |                 |            |       | 0.8        | v        |

| V <sub>ou1(1)</sub>    | Logical 1 output<br>voltage                                                                         | V <sub>CC</sub> = MIN,<br>I <sub>load</sub> = -400µA          | V <sub>in</sub> - 0 8V,                          |                 | 2.4        | 3.3   |            | v        |

| V <sub>out(0)</sub>    | Logical 0 output<br>voltage                                                                         | V <sub>CC</sub> <sup>e</sup> MIN,<br>I <sub>sink</sub> = 16mA | V <sub>in</sub> 727,                             |                 |            | 0.22  | 0.4        | v        |

| l <sub>in(0)</sub>     | Logical O level input<br>current (each input)                                                       | V <sub>CC</sub> = MAX,                                        | V <sub>in</sub> - 0.4V                           |                 |            |       | -1.6       | mA       |

| hn(1)                  | Logical 1 level input<br>current                                                                    | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX,              | V <sub>in</sub> - 2.4V<br>V <sub>in</sub> - 5.5V |                 |            |       | 40<br>1    | µА<br>mA |

| '03                    | Short circuit output<br>current t                                                                   | VCC = MAX                                                     |                                                  | \$5404<br>N7404 | -20<br>-18 |       | -55<br>-55 | mA       |

Series 900/900E

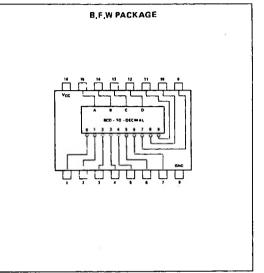

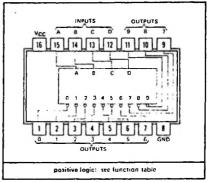

#### BCD-TO-DECIMAL DECODER/DRIVER WITH | S5445 **OPEN COLLECTOR HIGH VOLTAGE OUTPUTS**

PIN CONFIGURATIONS

\$5445-F,W + \$54145-F,W + N7445-B+ N74145-B

#### S54145 N7445 DIGITAL 54/74 TTL SERIES | N74145

#### DESCRIPTION

The 54/7445 and 54/74145 BCD-to-Decimal Decoder/Driver is a TTL MSI array. It features standard TTL inputs and high voltage, high current (80mA) outputs. The 54/7445 minimum output breakdown is 30 volts and the 54/74145 minimum output breakdown is 15 volts.

#### LOGIC DIAGRAM

NOTE: 1. These voltage values are with respect to network ground terminal.

#### TRUTH TABLE

|   | 11 | NPUTS |     |   |   |   |   | our | PUTS |     |   |     |    |

|---|----|-------|-----|---|---|---|---|-----|------|-----|---|-----|----|

| D | С  | В     | A   | Q | 1 | 2 | 3 | 4   | 5    | 6   | 7 | 8   |    |

| 0 | 0  | 0     | O I | 0 | 1 | 1 | 1 | 1   | 1    | 1   | 1 | 1   | Т  |

| 0 | 0  | 0     | 1   | 1 | 0 | 1 | 1 | 1   | 1    | [1] | 1 | 1   |    |

| 0 | 0  | 1     | 0   | 1 | 1 | 0 | 1 | 1   | 1    | 1   | 1 | [ 1 | 1  |

| 0 | 0  | 1     | 1   | 1 | 1 | 1 | 0 | 1   | 1    | 1   | 1 | 1   |    |

| 0 | 1  | 0     | 0   | 1 | 1 | 1 | 1 | 0   | 1    | 1   | 1 | 1   |    |

| 0 | 1  | 0     | 1   | 1 | 1 | 1 | 1 | 1   | 0    | 1   | 1 | 1   |    |

| 0 | 1  | 1     | 0   | 1 | 1 | 1 | 1 | 1   | 1    | 0   | 1 | 1   |    |

| 0 | 1  | 1     | 1   | 1 | 1 | 1 | 1 | 1   | 1    | 1   | 0 | 1   |    |

| 1 | 0  | 0     | 0   | 1 | 1 | 1 | 1 | 1   | 1    | 1   | 1 | 0   |    |

| 1 | 0  | 0     | 1   | 1 | 1 | 1 | 1 | 1   | 1    | 1   | 1 | 1   |    |

| 1 | 0  | 1     | 0   | 1 | 1 | 1 | 1 | 1   | 1    | 1   | 1 | 1   |    |

| 1 | 0  | 1     |     | 1 | 1 | 1 | 1 | 1   | 1    | 1   | 1 | 1   |    |

| 1 | 1  | 0     | 0   | 1 | 1 | 1 | 1 | 1   | 1    | 1   | 1 | 1   |    |

| 1 | 1  | 0     | 1   | 1 | 1 | 1 | 1 | 1   | 1    | 1   | 1 | 1   |    |

| 1 | 1- | 1     | 0   | 1 | 1 | 1 | 1 | 1   | 1    | 1   | 1 | 1   | İ. |

| 1 | 1  | 1     | 1 1 | 1 | 1 | 1 | 1 | 1   | 1    | 1   | 1 | 1   |    |

#### RECOMMENDED OPERATING CONDITIONS

| 1 |                                              |                         | MIN  | NOM | MAX  | UNIT |   |

|---|----------------------------------------------|-------------------------|------|-----|------|------|---|

|   | Supply Voltage V <sub>CC</sub> (See Note 1): | S5445, S54145 Circuits  | 4.5  | 5   | 5.5  | V 1  | Ĺ |

|   |                                              | N7445, N74145 Circuits  | 4.75 | 5   | 5.25 | V    | Ĺ |

|   | Voltage on any Output                        | S5445, N7445 Circuits   |      |     | 30   | V    | • |

|   |                                              | S54145, N74145 Circuits |      |     | 15   | v    |   |

|   |                                              |                         |      |     |      |      | 1 |

TTL MSI

#### TYPES SN5442A THRU SN5444A, SN54L42 THRU SN54L44, SN7442A THRU SN7444A, SN74L42 THRU SN74L44 4-LINE-TO-10-LINE DECODERS (1-OF-10) BULLETIN NO. DLS 7211861, DECEMBER 1972

#### '42A, 'L42... BCD-TO-DECIMAL '43A, 'L43... EXCESS-3-TO-DECIMAL '44A, 'L44... EXCESS-3-GRAY-TO-DECIMAL

Also for Application as 4-Line-to-16-Line Decoders 3-Line-to-8-Line Decoders

Diode-Clamped Inputs

| • <b>D</b>                  |                              |                               |

|-----------------------------|------------------------------|-------------------------------|

| TYPES                       | TYPICAL<br>POWER DISSIPATION | TYPICAL<br>PROPAGATION DELAYS |

| 42A 43A 44A<br>L42 L43, L44 |                              | 17 ns<br>49 ns                |

#### description

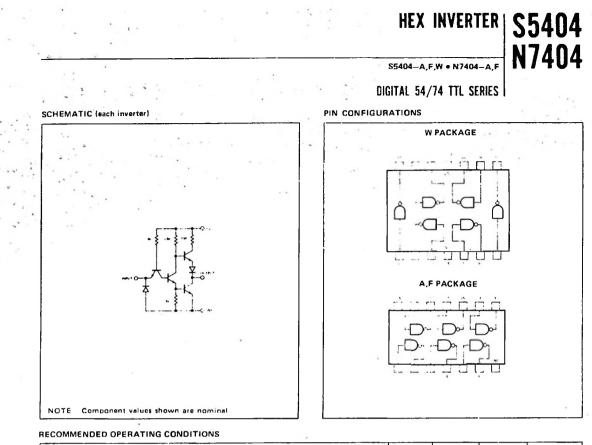

These monolithic decimal decoders consist of eight inverters and ten four-input NAND gates. The inverters are connected in pairs to make BCD input data available for decoding by the NAND gates. Full decoding of valid input logic ensures that all outputs remain off for all invalid input conditions.

The '42A and 'L42 BCD to decimal decoders, the '43A and 'L43 excess-3-to-decimal decoders, and the

SN54'/SN74'...J, N, OF W PACKAGE SN54L'/SN74L'...J OF N PACKAGE (TOP VIEW)

'44A and 'L44 excess-3-gray-to-decimal decoders feature familiar transistor-transistor-logic (TTL) circuits with inputs and outputs which are compatible for use with other TTL and DTL circuits. D-c noise margins are typically one volt.

The 'L42, 'L43, 'L44 decoders are designed specifically for power-critical or battery-operated systems. The '42A, '43A, and '44A decoders are intended for higher-performance systems especially new designs, where power is not critical. For ultra-high performance and:or speed-critical memory decoders, the SN54S138/SN74S138 and SN54S139-SN74S139 are recommended.

|        |    |     |        |      |    |      |        |     |      |        | TION 1 |       |   |    |   |     |      |      |     |   |   |   |

|--------|----|-----|--------|------|----|------|--------|-----|------|--------|--------|-------|---|----|---|-----|------|------|-----|---|---|---|

|        |    |     | , "L42 |      |    |      | . 'L43 |     |      | '44A,  |        |       |   |    |   |     |      | TYPE |     |   |   |   |

| NO.    |    | BCD | NPU    | T    | EX | CESS | -3-INI | PUT | EXCE | SS 3-0 | IRAY   | INPUT |   |    |   | DEC | IMAL | . ou | PUT |   |   |   |

|        | 0  | С   | 8      | _ A  | 0  | с    | В      | _A  | 0    | С      | 8      | A     | 0 | 1  | 2 | 3   | 4    | 5    | _6  | 7 | 8 | 9 |

| 0      | L  | L   | L      | L    | L  | L    | н      | н   | ιL   | L      | н      | L     | L | н  | н | н   | н    | н    | н   | н | н | н |

| 1      | L. | L   | L      | н    | L  | н    | L      | L   | L    | н      | н      | L     | н | L  | н | н   | н    | н    | н   | н | н | н |

| 2      | L  | L   | н      | L    | L  | н    | L      | н   | L    | н      | н      | н     | н | н  | L | н   | н    | н    | н   | н | н | н |

| 3      | L  | L   | н      | н    | L  | н    | н      | L   | L    | н      | L      | н     | н | н  | н | L   | н    | н    | н   | н | н | H |

| 4      | L  | н   | L      | L    | L  | н    | н      | н   | L    | н      | L      | ι     | н | н  | н | н   | L    | н    | н   | н | н | H |

| 5      | L  | н   | L      | н    | н  | L    | L      | L   | н    | н      | L      | L     | н | н  | н | н   | н    | L    | н   | н | н | н |

| 6      | L  | н   | н      | L    | н  | L    | L,     | н   | н    | н      | L      | н     | н | н  | н | н   | н    | н    | L   | н | н | н |

| 7      | L  | н   | н      | н    | н  | L    | н      | L   | н    | н      | н      | н     | н | н  | н | н   | н    | н    | н   | L | н | н |

| 8      | н  | L   | L      | L    | н  | L    | н      | н   | н    | н      | н      | L     | н | н  | н | н   | н    | н    | н   | н | L | н |

| 9      | н  | L   | L      | н    | н  | н    | L      | L   | н    | L      | н      | L     | н | н  | н | н   | н    | н    | н   | н | н | L |

|        | н  | L   | н      | L    | н  | н    | L      | н   | н    | L      | н      | н     | н | н  | н | н   | н    | н    | н   | н | н | H |

| 0      | н  | L   | н      | н    | н  | н    | н      | L   | н    | L      | L      | н     | н | н  | н | н   | н    | н    | н   | н | н | н |

| F      | н  | н   | L      | . L. | н  | н    | н      | н   | н    | L      | L      | L     | н | н  | н | н   | н    | н    | н   | н | н | н |

| NVALID | н  | н   | L      | н    | ι  | L    | L      | L   | L    | ī      | ĩ      | 1     | н | н  | н | н   | н    | н    | н   | н | н | н |

| -      | н  | н   | н      | L    | L. | L    | L      | н   |      |        |        | н     | н | н. | н | н   | н    | н    | н   | н | н | н |

|        | н  | н   | н      | н    | L. | L    | н      |     | -    | -      | н      | н     | н | н  | н | н   | н    | н    | н   | н | н | н |

" " on anel. L . low level

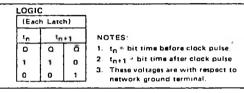

## QUADRUPLE BISTABLE LATCH | S5475

## 55475-B • N7475-B N7475

#### DIGITAL 54/74 TTL SERIES

#### PIN CONFIGURATIONS

#### DESCRIPTION

The S5475B/N7475B is a monolithic, quadruple, bistable latch with complementary Q and  $\vec{Q}$  outputs. Information present at a data (D) input is transferred to the Q output when the clock is high, and the Q output will follow the data input as long as the clock remains high. When the clock goes low, the information (that was present at the data input at the time the transition occurred) is retained at the Q output until the clock is permitted to go high.

This latch is ideally suited for use as temporary storage for binary information between processing units and input/output or indicator units.

#### TRUTH TABLE

#### SCHEMATIC (each latch)

#### RECOMMENDED OPERATING CONDITIONS

|                                                          | MIN  | NOM | MAX  | UNIT |

|----------------------------------------------------------|------|-----|------|------|

| Supply Voltage VCC (See Note 3): 55475 Circuits          | 4.5  | 5   | 5.5  | v    |

| N7475 Circuits                                           | 4.75 | 5   | 5.25 | v    |

| Normalized Fan-Out from Outputs                          |      |     | 10   |      |

| Operating Free-Air Temperature Range, TA: S5475 Circuits | -55  | 25  | 125  | °C   |

| N7475 Circuits                                           | 0    | 25  | 70   | °C   |

#### ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

|                    | PARAMETER                                                                    | 1                      | EST CONDITIONS'  | MIN | TYP" MAX | UNIT |

|--------------------|------------------------------------------------------------------------------|------------------------|------------------|-----|----------|------|

| V <sub>10(1)</sub> | Input voltage required<br>to ensure logical 1 level<br>at any input terminal | V <sub>CC</sub> * MIN  | +                | 2   |          | . v  |

| V <sub>in(0)</sub> | Input voltage required<br>to ensure logical O level<br>at any input terminal | V <sub>CC</sub> = MIN  |                  |     | 0.8      | v    |

| Vout(1)            | Logical 1 output voltage                                                     | V <sub>CC</sub> * MIN, | 1 load ~ -400µ A | 24  |          | v    |

| Vout(0)            | Logical 0 output voltage                                                     | V <sub>CC</sub> = MIN. | Isink = 16mA     |     | 0.4      | v    |

#### MONOSTABLE MULTIVIBRATOR | N74121

#### N74121-A,F

#### DIGITAL 54/74 TTL SERIES

DESCRIPTION

This monolithic TTL monostable multivibrator features d-c triggering from positive or gated negative-going inputs with inhibit facility. Both positive and negative-going output pulses are provided with full fan-out to 10 normalized loads.

Pulse triggering occurs at a particular voltage level and is not directly related to the transition time of the input pulse. Schmitttrigger input circuitry for the B input allows jittler-free triggering from inputs with transition times as slow as 1 volt/second, providing the circuit with an excellent noise immunity of typically 1.2 volts. A high immunity to V<sub>CC</sub> noise of typically 1.5 volts is also provided by internal latching circuitry.

Once fired, the outputs are independent of further transitions on the inputs and are a function only of the timing components. Input pulses may be of any duration relative to the output pulse. Output pulse lengths may be varied from 40 nanoseconds to 40 seconds by choosing appropriate timing components. With no external timing components (i.e., pin (§) connected to pin (14), pins (10), (13) open) an output pulse of typically 30 nanoseconds is achieved which may be used as a dc triggered reset signal. Output rise and fall times are TTL compatible and independent of pulse length,

Pulse width is achieved through internal compensation and is virtually independent of  $V_{CC}$  and temperature. In most applications, pulse stability will only be limited by the accuracy of external timing components.

Jitter-free operation is maintained over the full temperature and V<sub>CC</sub> range for more than six decades of timing capacitance (10 pF to 10µF) and more than one decade of timing resistance (2kΩ to 40kΩ). Throughout these ranges, pulse width is defined by the relationship t<sub>p</sub>|out) = C<sub>T</sub> R<sub>T</sub> loge 2.

#### TRUTH TABLE

|          | т  | 1+1 INPU | •  |   | INPUT |    |

|----------|----|----------|----|---|-------|----|

| Ουτρυτ   | 8  | A2       | A1 | 8 | A2    | A1 |

| len ti t | 1  | 1        | 1  | ٥ | 1     | 1  |

| hon-te-t | ٥  | ×        | 0  | 1 | x     | 0  |

| Inhibit  | 0  | o        | ×  | 1 | 0     | ×  |

| One Shut | 1  | ×        | o  | 0 | x     | 0  |

| Gee Shot | 1  | 0        | ×  | ٥ | 0     | ×  |

| One Shot | 1  | o        | ×  | 1 |       | 1  |

| Une Shut |    | ×        | 0  | 1 | 1     | 1  |

| lap-1-1  | o  | ,        | ×  | 0 | 0     | ×  |

| labibit  | a  | ×        | 1  | a | ×     | 0  |

| ion-not  | 1  | 1        | 1  | 1 | U     | ×  |

| Inf-pd   | 1  | 1        | 1  | 1 | ×     | 0  |

| inh-ba   | u  | 0        | ×  | a | ,     | 1  |

| Int-bet  | ۰o | ×        | a  | a |       | ,  |

Circuit performance is achieved with a nominal power dissipation of 90 milliwatts at 5 volts (50% duty cycle) and a quiescent dissipation of typically 65 milliwatts.

Duty cycles as high as 90% are achieved when using  $R_T$  - 40k $\Omega$ . Higher duty cycles are achievable if a certain amount of pulse-width jitter is allowed.

#### **PIN CONFIGURATIONS**

- A1 and A2 are negative-edge-triggered logic inputs, and will trigger the one shot when either or both go to logical 0 with B at logical 1.

- B is a positive Schmitt-trigger input for slow edges or level detection, and will trigger the one shot when B goes to logical 1 with either A1 or A2 at logical 0. (See Truth Table)

- External timing capacitor may be connected between pin

(positive) and pin

With no external capacitance, an output pulse width of 30ns is obtained typically.

- To use the internal timing resistor (2kΩ nominal), connect pin (9) to pin (14).

- To obtain variable pulse width connect external variable resistance between pin (9) and pin (4). No external current limiting is needed.

- For accuraté repeatable pulse widths connect an external resistor between pin (1) and pin (14) with pin (9) open-circuit.

- 7.  $t_n = time before input transition.$

- 8. t<sub>n+1</sub> = time after input transition.

- 9. x indicates that either a logical 0 or 1, may be present.

Series 900/900E

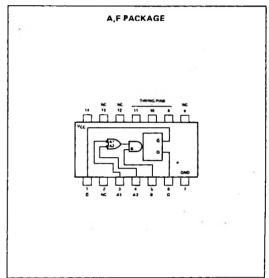

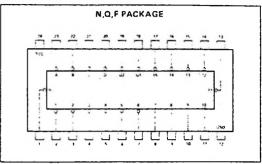

# 4-LINE TO 16 LINE DECODER/DEMULTIPLEXER S54154-N.O.F • N74154-N N74154

#### DIGITAL 54/74 TTL SERIES

PIN CONFIGURATIONS

#### LOGIC DIAGRAM

DESCRIPTION

strobe input is held low.

The 54/74154 decodes 4 binary-coded inputs to one of 16 mutually

exclusive outputs when each of the two strobe inputs are low. The demultiplexing function is achieved by using the 4 input lines for

output addressing and data from one strobe input while the other

#### TRUTH TABLE

|    | - 11 | NPU | τs |    |   |    |   |   |   |   |   | c   | UTP | UTS |   |    |    |    |    |    |    |

|----|------|-----|----|----|---|----|---|---|---|---|---|-----|-----|-----|---|----|----|----|----|----|----|

| G1 | G2   | D   | С  | B  | Α | 0  | 1 | 2 | 3 | 4 | 5 | 6   | 7   | 8   | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| L  | L    | L   | L  | L  | L | L  | н | н | н | н | н | н   | н   | н   | н | н  | н  | н  | н  | н  | н  |

| L  | L    | L   | L  | L  | н | н  | L | н | н | н | н | н   | н   | н   | н | н  | н  | н  | н  | н  | н  |

| L  | L    | L   | L  | н  | L | н  | н | L | н | н | н | н   | н   | н   | н | н  | н  | н  | н  | н  | н  |

| L  | L    | L   | L  | н  | н | н  | н | н | L | н | н | н   | н   | н   | н | н  | н  | н  | н  | н  | н  |

| L, | L    | L   | н  | L  | L | н  | н | н | н | L | н | н   | н   | н   | н | н  | н  | н  | н  | н  | н  |

| L  | L.   | L   | 'н | L  | н | н  | н | н | н | н | L | н   | н   | н   | н | н  | н  | н  | н  | н  | н  |

| L  | L    | L   | н  | н  | L | н  | н | н | н | н | н | L   | н   | н   | н | н  | н  | н  | н  | н  | н  |

| L  | L    | L   | н  | н  | н | н  | н | н | н | н | н | н   | L   | н   | н | н  | н  | н  | н  | н  | н  |

| L  | L.   | н   | L  | L  | L | н  | н | н | н | н | н | . н | н   | L   | н | н  | н  | н  | н  | н  | н  |

| L  | L    | н   | L  | L  | н | н  | н | н | н | н | н | н   | н   | н   | L | н  | н  | н  | н  | н  | н  |

| L  | L    | н   | L  | н  | L | н  | н | н | н | н | н | н   | н   | н   | н | L  | н  | н  | н  | н  | н  |

| L  | L    | н   | L  | н  | н | н  | н | н | н | н | н | н   | н   | н   | н | н  | L  | н  | н  | н  | н  |

| L  | L    | н   | н  | L. | L | н  | н | н | н | н | н | н   | н   | н   | н | н  | н  | L  | н  | н  | н  |

| L  | L    | н   | н  | L  | н | ļн | н | н | н | н | н | н   | н   | н   | н | н  | н  | н  | L  | н  | н  |

| L  | L    | н   | н  | н  | L | н  | н | н | н | н | н | н   | н   | н   | н | н  | н  | н  | н  | L  | н  |

| L  | L    | н   | н  | н  | н | н  | н | ы | н | н | н | н   | н   | н   | н | н  | н  | н  | н  | н  | L  |

| L  | н    | ×   | х  | х  | x | н  | н | н | н | н | н | н   | н   | н   | н | H  | н  | н  | н  | н  | н  |

| н  | L    | ×   | х  | х  | x | н  | н | н | н | н | н | н   | н   | н   | н | н  | н  | н  | н  | н  | н  |

| н  | н    | x   | ×  | x  | x | н  | н | н | н | н | н | н   | н   | н   | н | H  | н  | н  | н  | н  | н  |

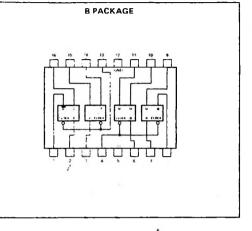

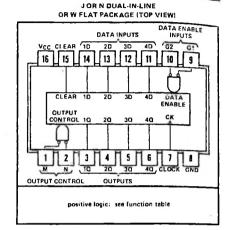

#### TYPES SN54173, SN74173 4-BIT D-TYPE REGISTERS WITH 3-STATE OUTPUTS BULLETIN NO. DLS 7211721 MAY 1972 BEVISED DECEMBER 1993

- Three-State Outputs Interface Directly with System Bus

- Gated Output-Control Lines for Enabling or Disabling the Outputs

- Fully Independent Clock Virtually Eliminates Restrictions for Operating in One of Two Modes:

#### Parallel Load Do Nothing (Hold)

- Average Propagation Delay . . . 23 ns Typical

- Maximum Clock Frequency . . . 35 MHz Typical

- Power Dissipation . . . 250 mW Typical

- For Application as Bus Buffer Registers

#### description

TTL

MSI

The SN54173 and SN74173 four-bit registers include D-type flip flops featuring totem-pole three-state outputs capable of driving highly capacitive or relatively low-impedance loads. The high-impedance third state and increased high-logic-level drive provide these flip-flops with the capability of being connected directly to and driving the bus lines in a bus-organized system without need for interface or pull-up components. For applications not requiring three-state outputs, the SN54174 or SN74174 hex D-type flip-flop can be used for a 33% reduction in package count and a 40% reduction in power, or the SN54175 or SN74175 quadruple D-type flip-flop can be used for a similar reduction in power.

Gated enable inputs are provided on the SN54173 and SN74173 for controlling the entry of data into the flip-flops. When both data-enable inputs are low, data at the D inputs are loaded into their respective flip-flops on the next positive transition of the buffered clock input. Gate output control inputs are also provided. When both are low, the normal logic states (high or low levels) of the four outputs are

|       |       | INPUTS |        |      | OUTPUT           |

|-------|-------|--------|--------|------|------------------|

| CLEAR | CLOCK | DATA   | ENABLE | DATA |                  |

| CLEAH | CLUCK | G1     | G2     | 0    | u                |

| н     | ×     | x      | x      | ×    | L                |

| L     | L     | x      | x      | ×    | <u>a</u>         |

| L     | 1     | н      | x      | ×    | 00<br>00<br>00   |

| L     | 1     | x      | н      | ×    | - a <sub>0</sub> |

| L     | t (   | L      | L      | L    | L                |

| L     | +     | L      | L      | н    | н                |

FUNCTION TAR/

When either M or N (or both) is (are) high the output is disabled to the high-impedance state; however sequential operation of the flip-flops is not affected.

H = high level (steady state)

L = low level (steady state)

t = tow-to-high-level transition

X = irrelevant (any input including transitions)

Oo = the level of Q before the indicated steady-state input conditions were established.

available for driving the loads or bus lines. The outputs are disabled independently from the level of the clock by a high logic level at either output control input. The outputs then present a high impedance and neither load nor drive the bus line. Detailed operation is given in the function table.

Rated at -5.2 mA high-logic-level drive current, up to 128 of the SN74173 outputs may be connected to a common bus and still drive two Series 54/74 TTL normalized loads. Similarly, up to 49 of the SN54173 outputs can be connected to a common bus and drive one additional Series 54/74 TTL load. To minimize the possibility that two outputs will attempt to take a common bus to opposite logic levels, the output control circuitry is designed so that the average output disable times are shorter than the average output enable times by 10 nanoseconds. The SN54173 and SN74173 are guaranteed to accept clock input frequencies up to 25 MHz.

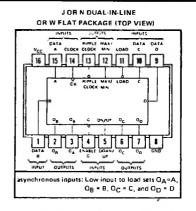

#### TYPES SN54190, SN54191, SN54LS190, SN54LS191, SN74190, SN74191, SN74LS190, SN74LS191 SYNCHRONOUS UP/DOWN COUNTERS WITH DOWN/UP MODE CONTROL BULLETIN NO DL 57211865, DECEMBER 1972

- Counts 8-4-2-1 BCD or Binary

- Single Down/Up Count Control Line

- Count Enable Control Input

- Ripple Clock Output for Cascading

- Asynchronously Presettable with Load Control

- Parallel Outputs

- Cascadable for n-Bit Applications

| TYPE                    | AVERAGE<br>PROPAGATION<br>DELAY | TYPICAL<br>MAXIMUM<br>CLOCK<br>FREQUENCY | TYPICAL<br>POWER<br>DISSIPATION |  |

|-------------------------|---------------------------------|------------------------------------------|---------------------------------|--|

| 190, 191                | 20 ns                           | 25 MHz                                   | 325 mW                          |  |

| 'LS190, ' <b>LS19</b> 1 | 20 ns                           | 25 MHz                                   | 90 mW                           |  |

|                         |                                 |                                          |                                 |  |

#### description

The '190, 'LS190, '191, and 'LS191 are synchronous, reversible up/down counters having a complexity of 58 equivalent gates. The '191 and 'LS191 are 4-bit binary counters and the '190 and 'LS190 are BCD counters. Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs change coincident with each other when so instructed by the steering logic. This mode of operation eliminates the output counting spikes normally associated with asynchronous (ripple clock) counters.

The outputs of the four master-slave flip-flops are triggered on a low-to-high-level transition of the clock input if the enable input is low. A high at the enable input inhibits counting. Level changes at the enable input should be made only when the clock input is high. The direction of the count is determined by the level of the down/up input. When low, the counter counts up and when high, it counts down.

These counters are fully programmable; that is, the outputs may be preset to either level by placing a low on the load input and entering the desired data at the data inputs. The output will change to agree with the data inputs independently of the level of the clock input. This feature allows the counters to be used as modulo-N dividers by simply modifying the count length with the preset inputs.

The clock, down/up, and load inputs are buffered to lower the drive requirement which significantly reduces the number of clock drivers, etc., required for long parallel words.

Two outputs have been made available to perform the cascading function: ripple clock and maximum/minimum count. The latter output produces a high-level output pulse with a duration approximately equal to one complete cycle of the clock when the counter overflows or underflows. The ripple clock output produces a low-level output pulse equal in width to the low-level portion of the clock input when an overflow or underflow condition exists. The counters can be easily cascaded by feeding the ripple clock output to the enable input of the succeeding counter if parallel clocking is used, or to the clock input if parallel enabling is used. The maximum/minimum count output can be used to accomplish look-ahead for high-speed operation.

Series 54' and 54LS' are characterized for operation over the full military temperature range of -55°C to 125°C; Series 74' and 74LS' are characterized for operation from 0°C to 70°C.

#### TTL MSI

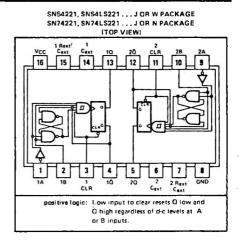

#### TYPES SN54221, SN54LS221, SN74221, SN74LS221 DUAL MONOSTABLE MULTIVIBRATORS WITH SCHMITT-TRIGGER INPUTS

BULLETIN NO. DL-S 7412027, MARCH 1974

- SN54221, SN54LS221, SN74221 and SN74LS221 Are Dual Versions of Highly Stable SN54121, SN74121 One-Shots on a Monolithic Chip

- Pulse-Width Variance Is Typically Less than ±0.5% for 98% of the Units

- SN54221 and SN74221 Demonstrate Electrical and Switching Characteristics That Are Virtually Identical to the SN54121, SN74121 One-Shots

- Pin-Out Is Identical to the SN54123 SN74123, SN54LS123, SN74LS123

- Overriding Clear Terminates Output Pulse

| TYPE      | TYPICAL<br>POWER<br>DISSIPATION | MAXIMUM<br>OUTPUT PULSE<br>LENGTH |

|-----------|---------------------------------|-----------------------------------|

| SN54221   | 130 mW                          | 21 s                              |

| SN 74221  | 130 mW                          | 28 5                              |

| SN54LS221 | 23 mW                           | 49 s                              |

| SN74LS221 | 23 mW                           | 70 s                              |

#### description

The '221 and 'LS221 are monolithic dual multivibrators with performance characteristics virtually identical to those of the '121. Each multivibrator features a negative-transition-triggered input and a positive-transition triggered input either of which can be used as an inhibit input.

Pulse triggering occurs at a particular voltage level and is not directly related to the transition time of the input pulse. Schmitt-trigger input circuitry (TTL hysteresis) for B input allows jitter-free triggering from inputs with transition rates as slow as 1 volt/second, providing the circuit with excellent noise immunity of typically 1.2 volts. A high immunity to VCC noise of typically 1.5 volts is also provided by internal latching circuitity.

Once fired, the outputs are independent of further transitions of the A and B inputs and are a function of the timing components, or the output pulses can be terminated by the overriding clear. Input pulses may be of any duration relative to the output pulse length may be varied from 35 nanoseconds to the maximum shown in the above table by choosing appropriate timing components. With  $R_{ext} = 2 \, k\Omega$  and  $C_{ext} = 0$ , an output pulse length may be used as a dio-triggered reset signal. Output rise and fall times are TTL compatible and independent of pulse length. Typical triggering and clearing sequences are illustrated as a part of the switching characteristics waveforms.

Pulse width stability is achieved through internal compensation and is virtually independent of  $V_{CC}$  and temperature. In most applications, pulse stability will only be limited by the accuracy of external timing components.

Jitter-free operation is maintained over the full temperature and V<sub>CC</sub> ranges for more than six decades of timing capacitance (10 pF to 10 µF) and more than one decade of timing resistance (2 kΩ to 30 kΩ for the SN54221, 2 kΩ to 40 kΩ for the SN54221, 2 kΩ to 10 kΩ for the SN54221, 2 kΩ to 10 kΩ for the SN54LS221, and 2 kΩ to 100 kΩ for the SN74221, 2 kΩ to 70 kΩ for the SN54LS221, and 2 kΩ to 100 kΩ for the SN74LS221). Throughout these ianges, pulse width is defined by the relationship: twrout) = CextRext In2 ≈ 0.7 CextRext. In circuits where noise cutoff is not critical, timing capacitance up to 1000 µF and timing resistance as low as 1.4 kΩ may be used. Also, the range of jitter-free output pulse widths is extended if V<sub>CC</sub> is

## (EACH MONOSTABLE)

| X        | X<br>H | x<br>x  | L       | н<br>н |

|----------|--------|---------|---------|--------|

| x        | x      | L       | L       | н      |

| н        | L      | •       | л       | v      |

| н        | 1 :    | H       | л       | ъ      |

| Also see |        | ption . | and swi | tching |

X = irrelevant

1 = transition from low to high level

\* transition from high to low level

#### TYPES SN54221, SN54LS221, SN74221, SN74LS221 DUAL MONOSTABLE MULTIVIBRATORS WITH SCHMITT-TRIGGER INPUTS

#### description (continued)

held to 5 volts and free-air temperature is 25°C. Duty cycles as high as 90% are achieved when using maximum recommended R<sub>T</sub>. Higher duty cycles are available if a certain amount of pulse-width jitter is allowed.

The variance in output pulse width from device to device is typically less than  $\pm 0.5\%$  for given external timing components. An example of this distribution for the '221 is shown in Figure 2. Variations in output pulse width versus supply voltage and temperature for the '221 are shown in Figure 3 and 4, respectively.

Pin assignments for these devices are identical to those of the SN54123/SN74123 or SN54LS123/SN74LS123 so that the '221 or 'LS221 can be substituted for those products in systems not using the retrigger by merely changing the value of  $R_{ext}$  and/or  $C_{ext}$ .

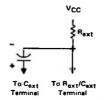

TIMING COMPONENT CONNECTIONS

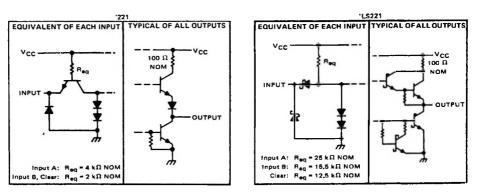

schematics of inputs and outputs

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)                         |  |  |   |  |  |  |  |  |    |     |     | . 71           |

|----------------------------------------------------------|--|--|---|--|--|--|--|--|----|-----|-----|----------------|

| Input voltage: SN54221, SN74221                          |  |  | , |  |  |  |  |  |    |     |     | . 5.5 \        |

| SN54LS221, SN74LS221                                     |  |  |   |  |  |  |  |  |    |     |     |                |

| Operating free-air temperature range: SN54221, SN54LS221 |  |  |   |  |  |  |  |  | _  | 65° | Ċt  | o 1 <b>25°</b> |

| SN74221, SN74LS221                                       |  |  |   |  |  |  |  |  |    | 0   | °c  | to 70°         |

| Storage temperature range                                |  |  |   |  |  |  |  |  | -1 | 65° | C t | ° 150 o        |

NOTE 1: Voltage values are with respect to the network ground terminal.

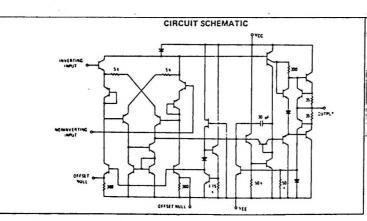

**OPERATIONAL AMPLIFIERS**

MC1741S MC1741SC

OPERATIONAL AMPLIFIER

MONOLITHIC SILICON

INTEGRATED CIRCUIT

ME

G SUFFIX TAL PACKAGE CASE 601

. . . ..

PI SUFFIX PLASTIC PACK AGE CASE 626 -MC1741SC Only1

....

ĩ

The MC1741S/MC1741SC is functionally equivalent, pin compatible, and possesses the same ease of use as the popular MC1741 circuit, yet offers 20 times higher slew rate and power bandwidth. This device is ideally suited for D-to-A converters due to its fast sattling time and high slew rate.

- High Slew Rate 10 V/µs Guaranteed Minimum

- No Frequency Compensation Required

- Short-Circuit Protection

- Offset Voltage Null Capability

- Wide Common-Mode and Differential Voltage Banges

- Low Power Consumption

- No Latch-Up

|                                                  |                                     | Va         |             |       |  |

|--------------------------------------------------|-------------------------------------|------------|-------------|-------|--|

| Aating                                           | Symbol                              | MC1741SC   | MC1741S     | Unit  |  |

| Power Supply Voltage                             | V <sub>C</sub> C<br>V <sub>EE</sub> | +18<br>-18 | •22<br>-22  | Vdc   |  |

| Differential Input Signal Voltage                | Vin                                 |            | Volta       |       |  |

| Common-Mode Input Voltage Swing (See Note 1)     | VICR                                | :          | Volts       |       |  |

| Output Short-Circuit Duration (See Note 2)       | τ,                                  | Cont       | ทมอนร       |       |  |

| Power Dissipation (Package Limitation)           | Po                                  | 1          |             | T     |  |

| Metal Package                                    |                                     | 6          | 80          | mvV   |  |

| Derate above TA = +25°C                          |                                     |            | m₩/ºC       |       |  |

| Plastic Dual In-Line Package                     |                                     | 6          | Wm          |       |  |

| Derate above T <sub>A</sub> = +25 <sup>o</sup> C |                                     |            | i 0         | mW/°C |  |

| Operating Temperature Range                      | Τ <sub>Α</sub>                      | 0 to +75   | -55 to +125 | °C    |  |

| Storage Temperature Range                        | T stg                               |            |             | °c    |  |

| Metal Package                                    |                                     | -65 1      | a • 150     |       |  |

| Plastic Package                                  | 1                                   | - 55 1     | o -125      |       |  |

Note 1 For supply voltages less their 215 Vdc, the absolute maximum input voltage is equal to the supply voltage

Note 2. Supply voltage equal to or less then 15 Vdc.

#### SECTION 5 - CIRCUIT DESCRIPTIONS

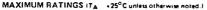

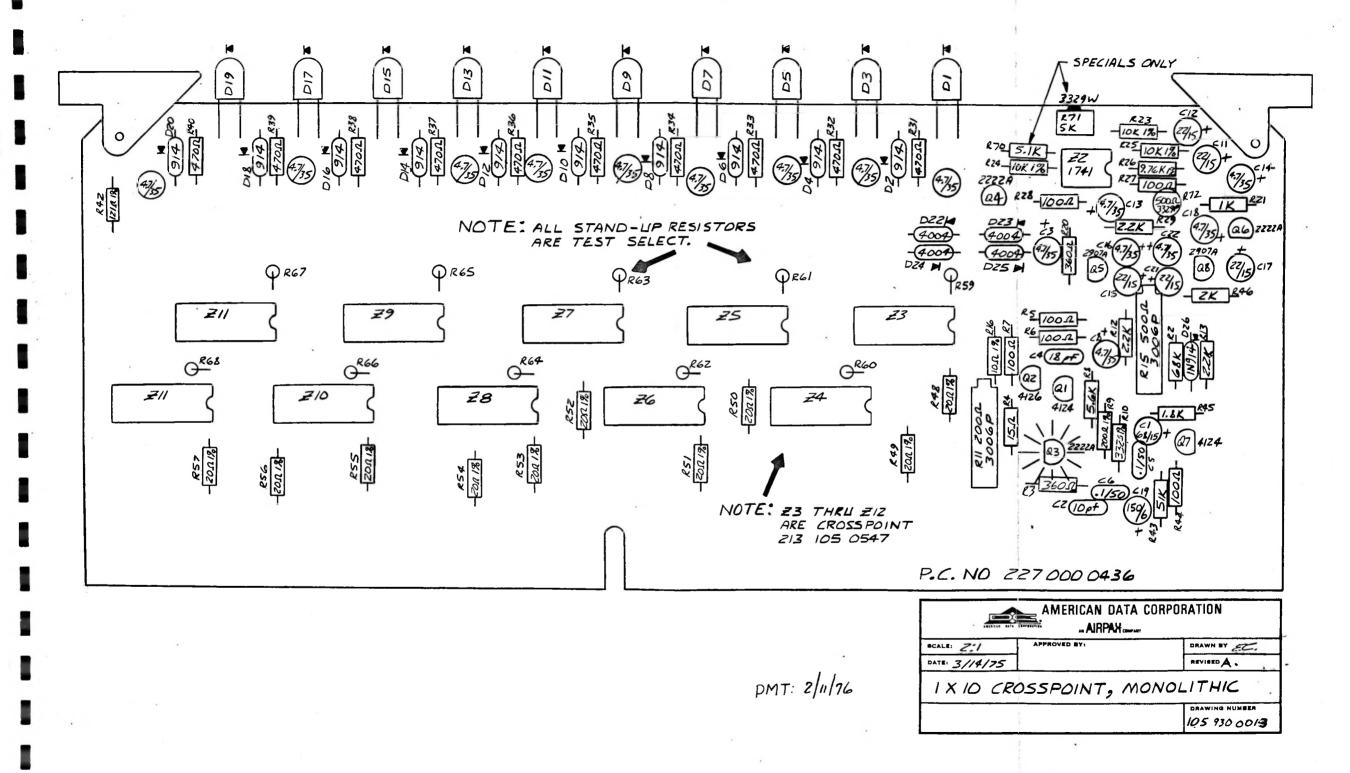

#### 1 x 10 Audio/Video Crosspoint Card

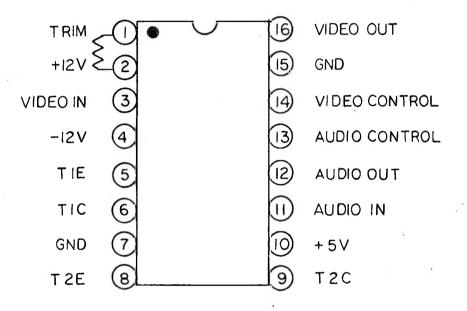

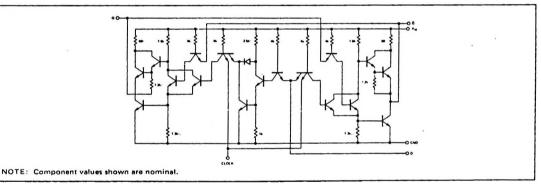

Please refer to drawing,  $1 \times 10$  Crosspoint, Monolithic - Model 9101M, Dwg. No. 995 930 0013.

<u>Purpose</u> - The  $1 \times 10$  card buffers and switches the audio input, buffers and switches the video input, and generates both a "row" tally and a "bus" tally output.

Description - A high input impedance (approximately 10 K ohms), differential input, audio amplifier provides over 60 dB of common mode rejection, converts the balanced audio signal to single-ended, and isolates the audio input line from the primary switching system. Resistors R17, R18 and R19 are used to terminate the balanced line. Resistors R24 and R26 can be changed according to the table shown on the reference drawing to vary the gain of the front-end audio amplifier.

A high input impedance (approximately 50 K ohms) video amplifier isolates the switching system from the video input signal which may be looped-through to other matrix boxes or to other equipment. This video amplifier has a gain of approximately 1.6 and functions as a high impedance input, very low output impedance buffer.

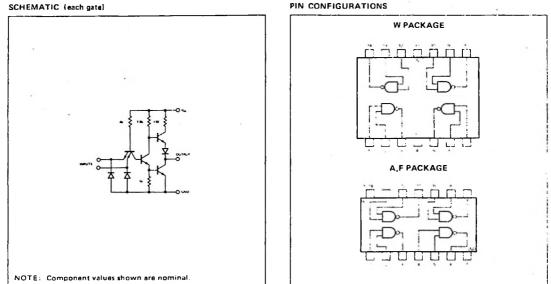

Switching of both audio and video is performed by a 16 pin dual-in-line integrated circuit developed by ADC especially for this purpose. Switching is completed when the control line(s) is pulled to matrix ground potential. At this time, two separate tally transistors are activated; one turns on a LED on the card indicating closure and functions as "row" tally output, the second is collector OR'd with corresponding transistors in other crosspoints to form "bus" tally.

Potentiometer R11 provides an approximate  $\pm 2^{\circ}$  phase shift adjustment. With a little care, all paths through the series 900/900E can be phased so that less than  $\pm 1^{\circ}$  of phase error exists between any path through the system.

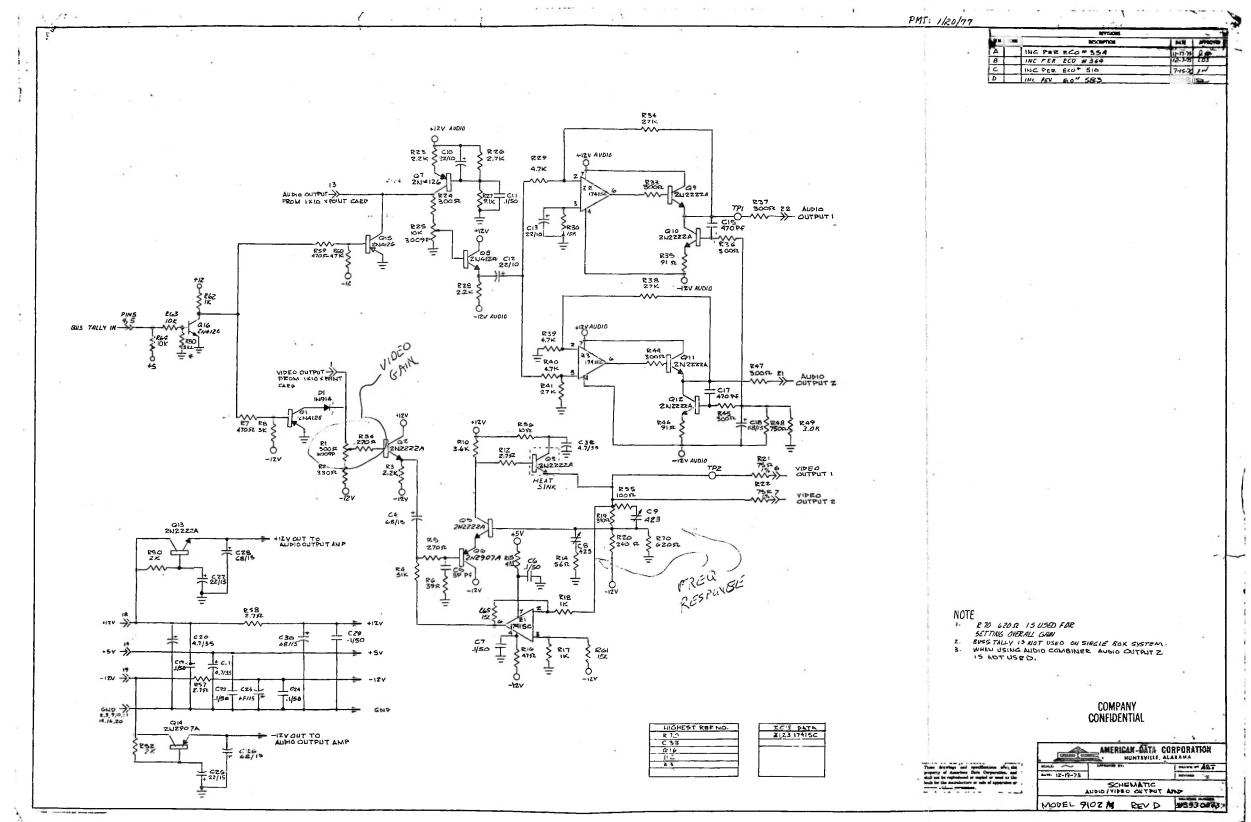

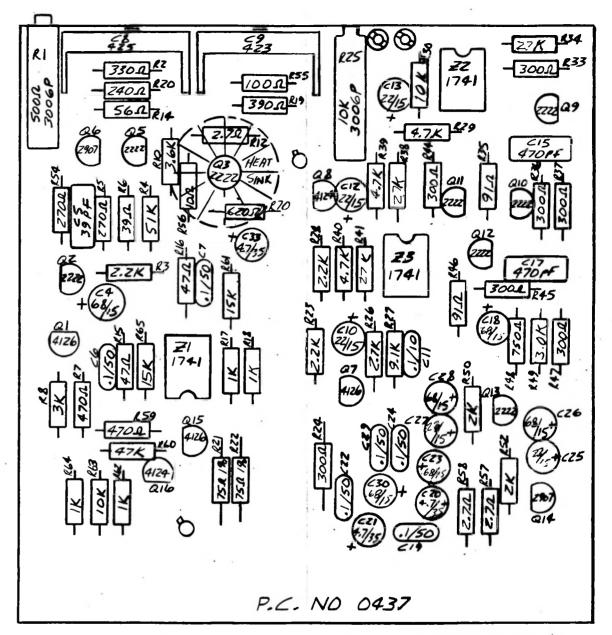

#### Audio/Video Output Amplifier

Please refer to drawing, Schematic, Audio/Video Output Amplifier - Model 9102M, Dwg. No. 995 930 0014.

<u>Purpose</u> - The audio/video output amplifier card provides the audio and video bus current sources (or load resistors). In addition, it provides a high impedance to the bus and a low output impedance.

Description – As each crosspoint is turned ON, the audio signal passes through the crosspoint and appears on the collector of Q7, the crosspoint current source. A transistor (Q15) is used as a "blind" crosspoint when there are no crosspoints ON in the bus served by that output amplifier. This prevents "popping" when switching a signal onto this bus. The audio signal on the collector of Q7 is divided by R25 (audio gain control). The integrated circuits Z2 and Z3 generate out-of-phase signal to drive the output transistors Q9 and Q11, which produces a balanced audio output.

The output stage of the ADC designed video crosspoint is an emitter follower whose emitter load is made up of Rl and R2 on the output amplifier. Ql is a clamping transistor to set the level (dc) at the input to the output amplifier when there are no other crosspoints ON on the bus. Potentiometer Rl is the video GAIN control. The video output amplifier incorporates a dc restoration circuit to maintain the back porch of the composite video signal near ground potential.

The audio amplifier has one balanced, 600 ohm output; the video output amplifier has two 75 ohm, single-ended outputs.

. .

. . . . .

. . . . . .

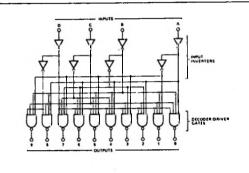

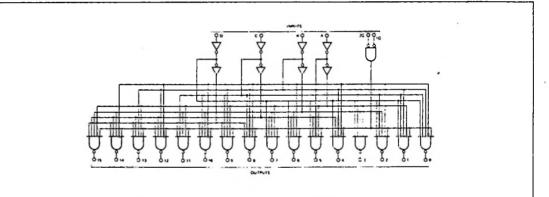

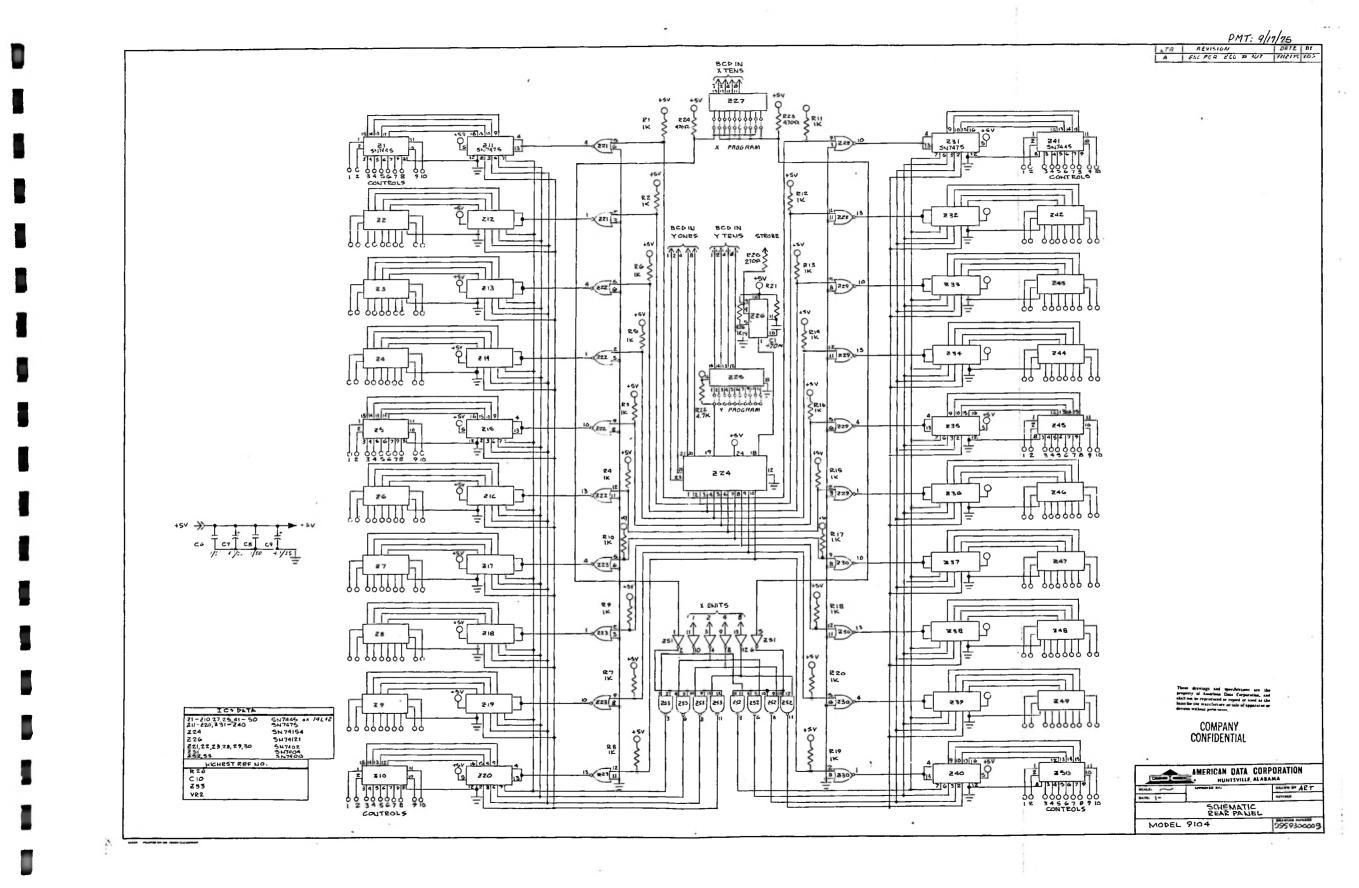

#### Matrix Control Logic

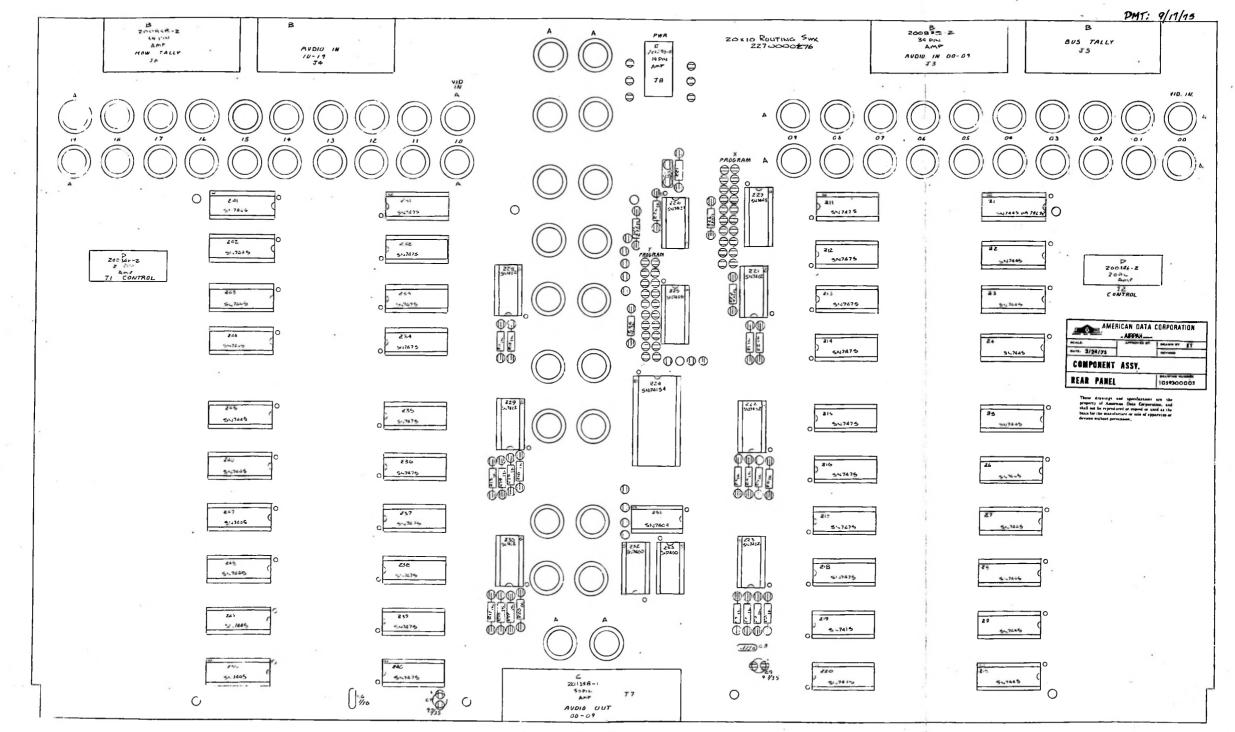

Please refer to drawing, Schematic, Rear Panel - Model 9104, Dwg. No. 995 930 0005.

<u>Purpose</u> - The rear panel of the series 900/900E matrix frame contains all the crosspoint control logic. This logic decodes incoming commands and causes the selected crosspoint control line to go to matrix ground.

<u>Description</u> - The series 900/900E matrix is divided into two 10 x 10 sections which ideally lend themselves to control by BCD characters (1-2-4-8). In normal operation, the matrix is set up by a series of 16-bit words made up of four 4-bit characters. These characters are called X-units, X-tens, Y-units and Y-tens. For a 20 x 10 matrix, the X-tens are decoded by Z27 to steer the four bits of X-units data to either the 0 - 9 side or the 10 - 20 side of the matrix. The outputs of Z27 are strappable on each matrix frame so that the units data can be steered in matrices with larger inputs. The matrix frame for inputs 21 - 40 would have straps on the 3 and 4 outputs of Z27.

The X data, of course, controls input while the Y data determines the output. To operate properly, both commands must be present. Y-units are decoded by Z24 to provide ten discrete outputs which gate the X-units data into the latches of the desired output bus. As you can see on the referenced drawing, there are a latch and decoder associated with each ten inputs on each output bus. Once the data is latched, it is decoded into one of ten discrete outputs by the decoder associated with that latch which, in turn, closes the associated crosspoint. Y-tens are decoded by Z25 and the output strapped to identify the matrix frame from an output point of view. Strapping the 1 output of Z25 to pin 19 of Z24, as an example, identifies outputs 1 - 10 and gates only the Y-units commands associated with those outputs to Z24.

A series of ten 16-bit words, therefore, can select the input (1 of 100) desired for each of ten output buses.

In addition to the method of control described above, it is possible, for example, to remove Z11 and install a dual-in-line connector and control the first half of the first bus with any 4-bit latched data. Also, Z1 can be removed and a dual-in-line connector

installed with ten discrete wires which can control the first half of output bus #1. Interlocks would have to be provided in the external control system to prevent turning on more than one crosspoint on a bus.

In normal operation, the control interface unit generates a series of 16-bit words and a strobe which are the command inputs to the series 900/900E matrix frame. The strobe pulse (derived from Vdrive) latches the Y-data into Z24 provided, of course, that it is not inhibited by the output of the Y-tens decoder. This provides vertical interval switching for the series 900/900E routing switches.

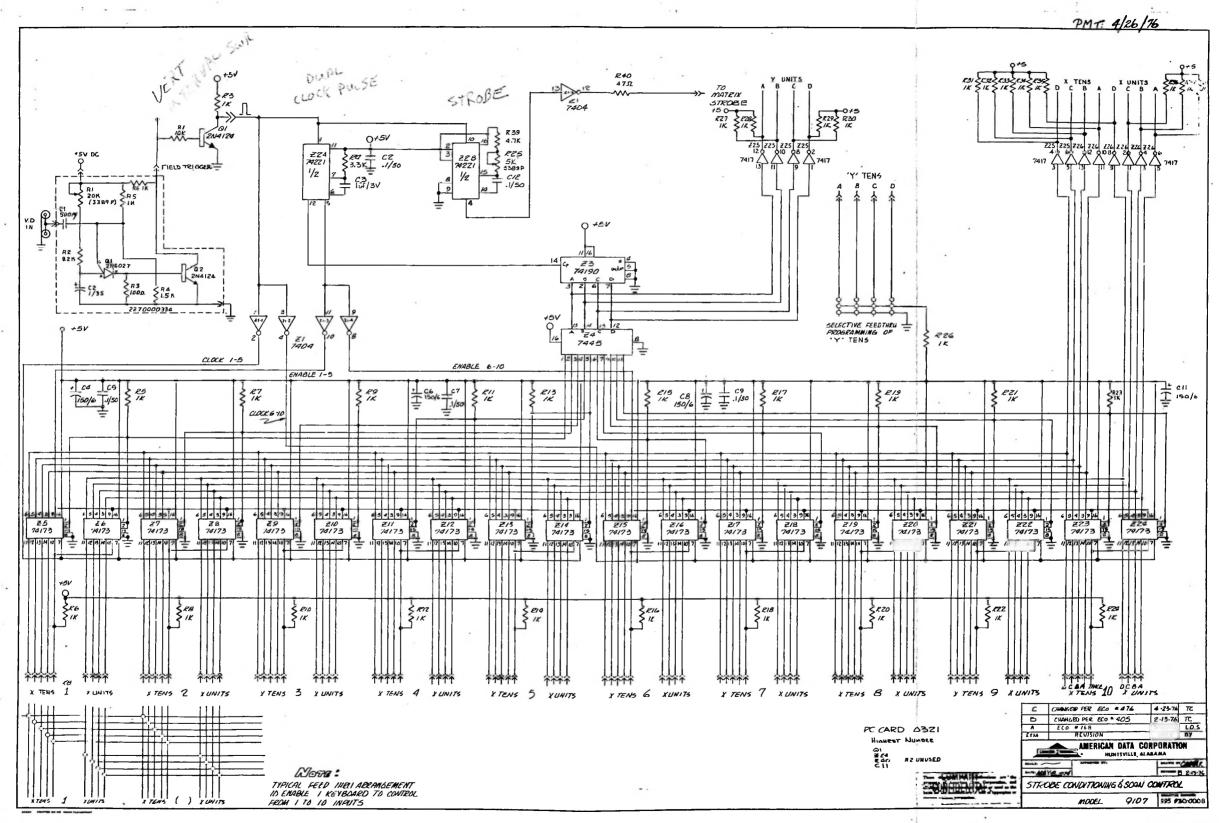

#### Control Interface

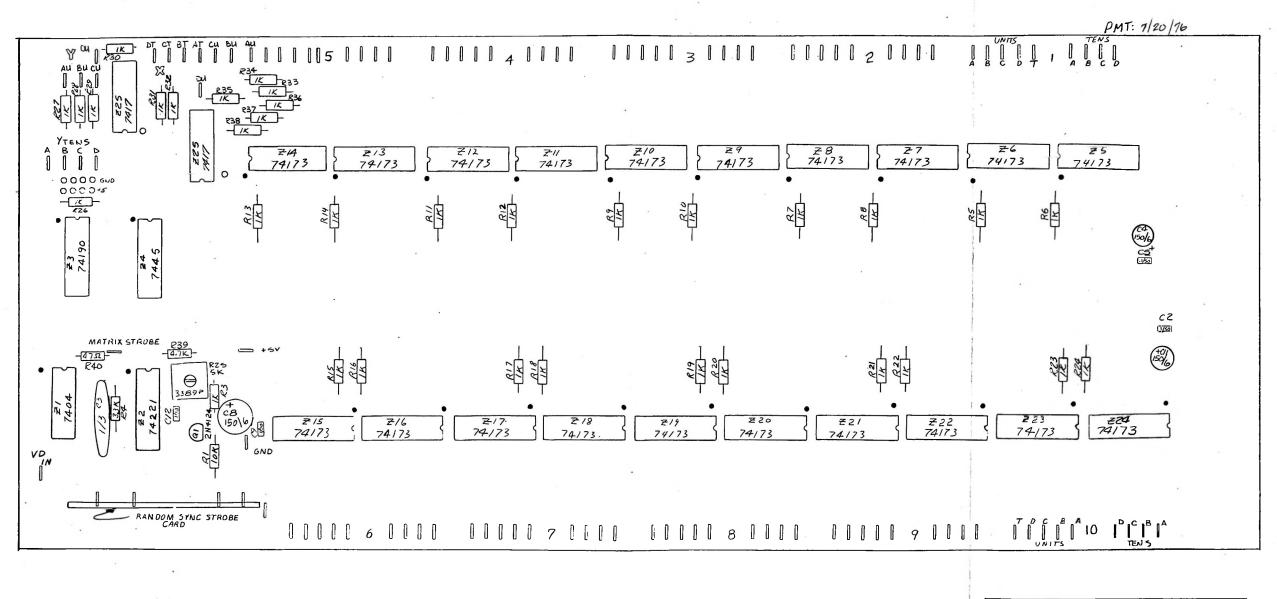

Please refer to drawing, Strobe Conditioning & Scan Control – Model 9107, Dwg. No. 995 930 0008.

<u>Purpose</u> - The series 900/900E control interface multiplexes inputs from all standard ADC control modules to generate a 16-bit BCD word and strobe pulse to control the series 900/900E matrix.

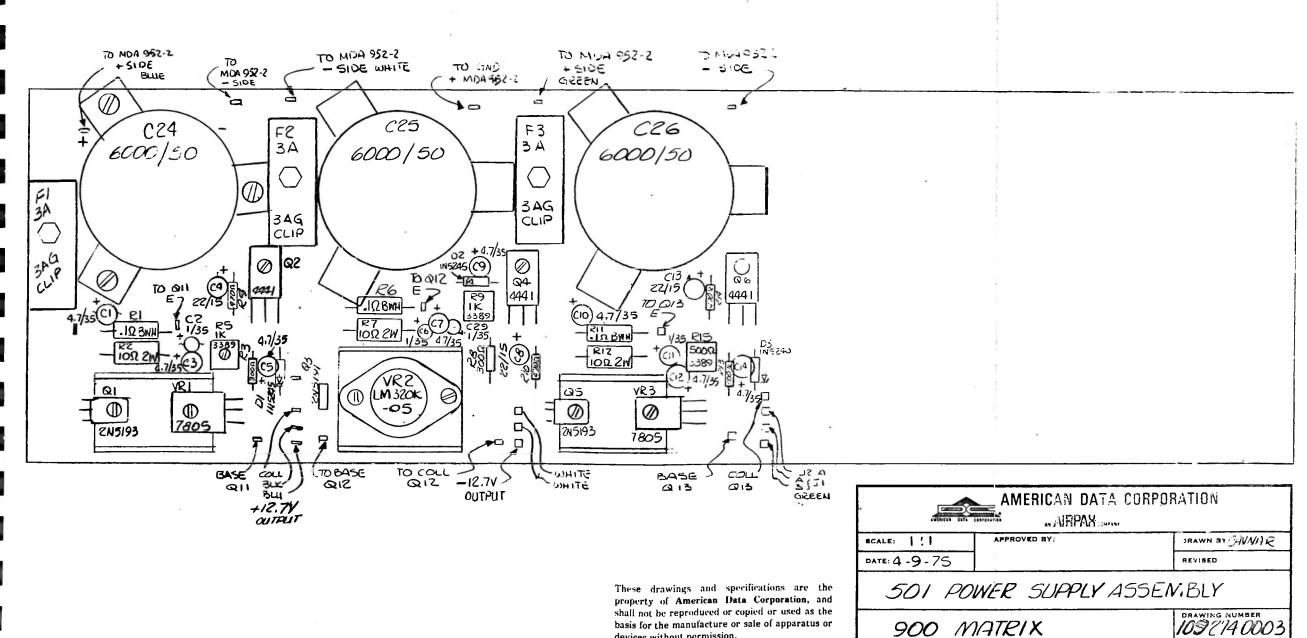

<u>Description</u> - All information transfer in the control interface is made under the control of one of two clock pulses. The first is a 60 Hz pulse derived from incoming V-drive, which makes all switching occur in the vertical interval. The second clock pulse source is a 60 Hz self-contained oscillator.

A one-shot multivibrator (Z2A) generates a dual clock pulse which first gates new information from the remote control units into the storage registers, then advances the Y-units counter (Z3).

The other side of Z2 (Z2B) creates a strobe pulse from the leading edge of V-drive, which is delayed by an amount determined by R25. This strobe pulse is normally set to occur two to four lines after the vertical sync.

Twenty tri-state 4-bit registers (SN74173's) are arranged in ten sets of 8-bits, which correspond to the ten output buses. Normally, each set of 8-bits represents the input selection (00 to 99) made by each discrete control panel and its associated TAKE button; however, inputs to the control unit may be paralleled for controlling more than a single output from a single control panel. New input select information is stored when a TAKE command and a clock pulse (from Z2A) occur simultaneously.

The Y-units counter also feeds a BCD to the one-of-ten decoder Z4 (SN7445) which controls the output state of the tri-state registers. Each time the Y-units counter advances, a new set of eight X-bits is selected. After a slight delay, the matrix is strobed; entering the new 16-bit control word into the series 900/900E matrix control logic. Each output bus of the matrix is updated every tenth V-drive pulse. This makes the maximum TAKE delay that can occur nine vertical interval periods (9 times 16.6 ms).

. . . . . . . . . . . . .

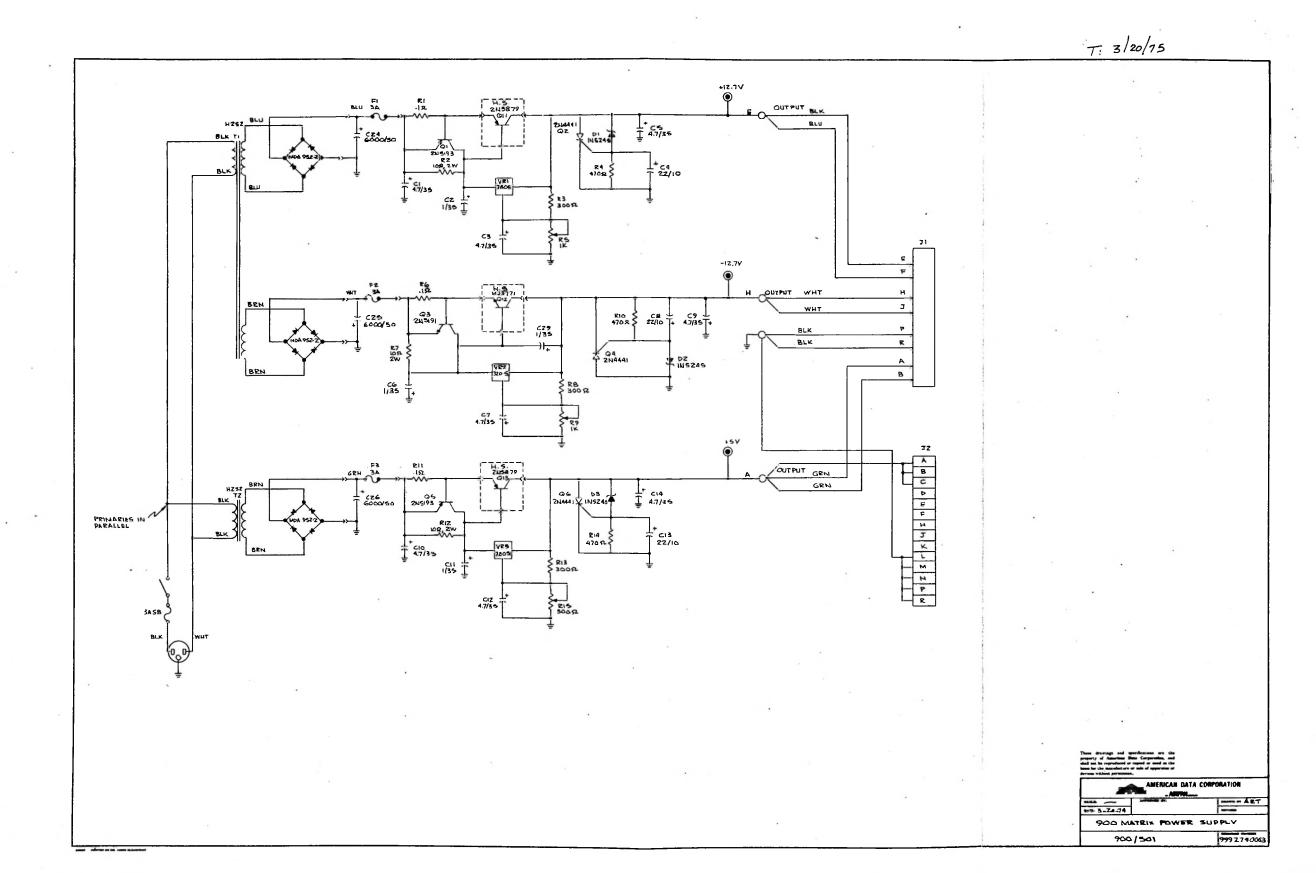

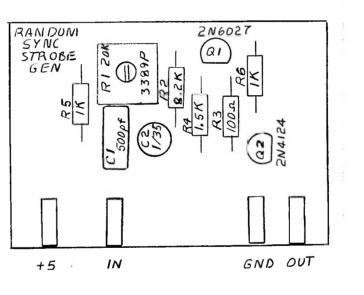

#### Power Supply

Please refer to drawing, 900 Matrix Power Supply - 900/501, Dwg. No. 999 274 0003.

<u>Purpose</u> - ADC provides a standard Model 501 power supply (for systems smaller than 20 x 20) or purchased supplies (Lambda or Hewlett Packard, normally) to supply the +12 voits, -12 volts and +6 volts required by the series 900/900E matrix systems. If your system has purchased supplies, please consult the manufacturer's instruction manual included in the system documentation.

<u>Description</u> - The ADC Model 501 supplies the three voltages (+12, -12, and +6) required by the series 900/900E matrix frame. All three power supplies in the Model 501 are fundamentally the same, therefore, only one will be explained. The rectified, filtered voltage on the plus end of C24 is the unregulated dc source. Fuse F1 protects against catastrophic failure in the event the current limit circuit (R1-Q1) fails to limit current flow. Transistor Q11 and voltage regulator VR1 form a standard voltage regulator. The output voltage can be adjusted by R5. Another safety feature is the "crowbar" circuit formed by D1-R4-Q2. In the unlikely event that the series regulator fails (shorts), and the output voltage starts to rise, the SCR (Q2) will fire, creating an effective short circuit across the output and causing F1 to blow. Q2 fires when the output voltage exceeds the drop across zener D1 (12 volts) by approximately 2 volts.

Each of the other supplies operates in much the same manner, being comprised of a raw dc supply, fuse, current limiter, series regulator, and an output "crow-bar" circuit.

Each output is metered by a switchable meter circuit.

#### SECTION 6 - MAINTENANCE

#### General Data

There are, in general, two aspects to maintaining the series 900/900E matrix and associated controls. These are preventive maintenance and servicing or troubleshooting in the event of failure. All ADC equipment is transistorized, therefore it requires very little preventive maintenance. The inevitable accumulation of dust should be removed periodically with a soft, long bristled brush, a vacuum cleaner (be sure that the power is OFF if hose end is metal), or a stream of low pressure air. An excessive ambient temperature level is certainly the greatest danger to electronic equipment. Although ADC equipment requires no special cooling, during preventive maintenance check the rack enclosure filters (if it has them) and rack ventilation entrance/exit points to insure that they are not obstructed.

ADC provides extender boards for the two PC boards in this equipment. Each card may be made more accessible by installing it on the extender board provided. The dc voltages present on the boards are low enough so that no potential shock hazard exists; but it is still necessary to guard against accidential shorts from tools and other metal (conductor) objects.

If it becomes necessary to replace any solid state components, precautions should be taken to avoid heat damage. The use of long-nosed pliers or other clip-on heat sinks is advised. Also, excessive heat may cause the actual copper PC board circuits to "peel off" the Gl0 glass epoxy boards. ADC recommends the small, pencil type soldering irons of 20 - 30 watts capacity to reduce the chance of damage to solid state components or the PC board itself.

One of the most effective means of removing the solder from the leads of the device being replaced is to use the so called "solder sponge" technique. ADC recommends the use of a rosin-dipped, tinned, copper braid manufactured by Alpha Industries, or equivalent. If this is not available, copper braid can be obtained by stripping the insulation off short pieces of coaxial cable and using the braided shield dipped in a rosin solution such as Alpha Industries Alpha Realiafoam #809 Flux. A clean, well-tinned soldering iron tip held against the rosin coated braid, which in turn is held against the solder area to be cleaned, will result in quick removal of

solder from this area with minimum possibility of heat damage.

Junction breakdown in transistors and diodes due to excessive current or heat will result in the junction's appearing to be short circuited or open circuited. This can be easily verified by an ohmmeter like the Simpson 260. To avoid the possibility of damaging a good component, set the meter on the ohms x 10 scale. With the knowledge that a forward biased diode presents a low impedance path and a reverse biased diode a high impedance path, you can quickly determine if a diode/transistor junction has failed in either of the two modes previously mentioned.

With the positive lead of the voltmeter on the anode of a silicon diode and the negative lead on the cathode (end with the band), you should read on the ohmmeter something less than 500 ohms, but not a short. Reversing the leads should result in a reading of greater than one megohm, but not an open.

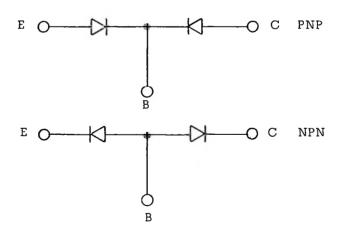

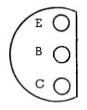

Transistors can be regarded as two diodes connected back-toback. The diode equivalent to PNP and NPN transistors is shown in Fig. 6-1.

Fig. 6-1 Diode Equivalent of Transistor

The bottom view of a typical transistor used by ADC is shown in Fig. 6-2.

#### Fig. 6-2 Bottom View of Typical Transistor

Using the technique previously explained for determining the condition of a diode, you can use the Simpson 260 (ohmmeter) to determine the condition of the "diode" junction in a transistor. Again, in the forward direction, the meter should read about 300 - 500 ohms, and in the reversed bias direction, over one megohm. In no case should the meter indicate a short or an open condition.